BSc FINAL YEAR THESIS PROJECTS

Proposed by the

Radar

Remote Sensing Group (RRSG)

2013

These topics are on the web at:

http://www.rrsg.uct.ac.za/proposals/

(The

web version includes a convenient topic listing and hyperlinks.)

Images on the top right indicate the theme

List of Topics

BSc FINAL YEAR THESIS PROJECTS

Evaluation of Gauss-Newton tracking algorithm

GOTO Pedestal Software for NetRAD

Analysis of target backscatter measurements

Radar signal processing on Rhino board

Forward-looking radar for a small satellite

RHG-1: Antenna with Reconfigurable Radiation Pattern for Wireless Sensor Networks

RHG-2: Antenna with Tunable Reflector Surface for Predator Tracking by Wireless Sensor Networks

RHG-3: Antenna for Predator Tracking Collar

RHG-4: X-band Antenna for Drone Project

RHG-5: X-band Substrate-integrated Waveguide (SIW) Filter for Drone Project

RHG-6: Quasi-lumped Element Microwave Filter Design for Multilayer Layouts

RHG-7: Quasi-lumped Element Directional Coupler Design for Multilayer Layouts

RHG-8: Quasi-lumped Element Dual-band Filter Design for Multilayer Layouts

Doppler Radar based Human Gait

Compressive Sampling for SAR Imaging

Cognitive Architecture on FPGA

Evolutionary algorithms to design the placement of SKA antennas

Error analysis of SKA Digital Backend (DBE)

The effect of nonlinear windowing on practical signal processing

Frequency domain Radar based target recognition..

Low cost ECG using android phone

Cognitive recognition based on brain architecture

Information geometry based target recognition

Topics Proposed by A. Van Der Byl

Simple ADC and DAC Interface for Rhino

CATEGORY: EMBEDDED SYSTEMS & SIGNAL PROCESSING

UTED – Ultrasonic Trajectory Estimation Device

RPSFSS – Raspberry Pi Sensor Fusion Security System

RWTM - Rhino Wireless Transceiver Module

SwaMURAy – Swapping Memory Unit for Radio Astronomy

PRTF - Populating the Rhino Toolflow Framework

mVAIS – Vision-based Alignment and Image transfer System

Porting of the Commensal Radar Processing Server.

VTED – Visual Trajectory Estimation Device

Golf Ball Launch Angle Calculator (GBLAC)

FLORA – Fynbos Leaf-based Online Recognition Application V.3

Implementation of Numberplate Recognition on the Raspberry PI Architecture

O2LD3P – Open-source & Open-plan Large-scale Dimensiones des 3 Printer (part A)

O2LD3P – Open-source & Open-plan Large-scale Dimensiones des 3 Printer (part B)

![]() “Bonsai House” – Bonsai greenhouse

environment control & monitoring system

“Bonsai House” – Bonsai greenhouse

environment control & monitoring system

WPGC – Wireless Pong Game Controlled

CATEGORY: HIGH PERFORMANCE COMPUTING & NETWORKING

MDPN – Mobile Database POS Network System

VTBA – Virtualization Technologies Benchmarking Analysis

Legacy Topics – l (ask before selecting)

LURCCI – Level-floor Undercover Robot Crawler Controlled by Internet (phase 1)

SPI-Ladder: an embedded system rapid prototyping strategy

Aerofoil Fluid Flow Simulation (AFFS)

BEC - Blocks to Embedded C code in a visual way

ESPPA - Embedded Systems Past Projects Archive.

NPBBS – Number Plate Based Billing Parking

Topics Proposed by M. Inggs

|

ID: |

MI-1 |

|

TITLE: |

Evaluation of Gauss-Newton tracking algorithm |

|

DESCRIPTION: |

Gauss-Newton or Polynomial tracking algorithm is a powerful tracking algorithm first proposed by UCT’s Dr. Norman Morrison. We have code which implements this algorithm. The student will be required to run exhaustive simulations for different types of trajectories to validate this algorithm. |

|

DELIVERABLES: |

Report describing results of experiments |

|

SKILLS/REQUIREMENTS: |

Good mathematical skills and ability to extend these. Programming in a language such as Python. |

|

EXTRA INFORMATION: |

|

|

AREA: |

Radar Signal processing. |

|

ID: |

MI-2 |

|

TITLE: |

L Band Radar antenna |

|

DESCRIPTION: |

We have a number of wire grid parabolic surfaces and theoretical designs of a printed circuit log periodic antenna for this surface. We would like to contruct, test, and optimise this antenna for 1300MHz. |

|

DELIVERABLES: |

Report and working hardware |

|

SKILLS/REQUIREMENTS: |

3rd year EM course, and further RF and microwave course experience. |

|

EXTRA INFORMATION: |

|

|

AREA: |

Electromagnetics |

|

ID: |

MI-3 |

|

TITLE: |

NetRAD Data Processing |

|

DESCRIPTION: |

UCT and UCL have been deploying a three node S Band pulse compression radar on extensive sea and land trials. Raw, uncompressed data is available, and needs to be processed using a script that is easy to operate. |

|

DELIVERABLES: |

Scripts for processing NetRad data. |

|

SKILLS/REQUIREMENTS: |

Signal processing and strong programming skills |

|

EXTRA INFORMATION: |

|

|

AREA: |

Radar signal processing |

|

ID: |

MI-4 |

|

TITLE: |

VHDL/Verilog Radar Block |

|

DESCRIPTION: |

We have developed the Rhino FPGA/Processor card. We wish to develop a block of VHDL / Verilog code to implement a full radar timing and waveform generator. |

|

DELIVERABLES: |

Working code, with verified timing. Demonstration on a FPGA prototyping card. |

|

SKILLS/REQUIREMENTS: |

FPGA programming skills |

|

EXTRA INFORMATION: |

http://www.rhino.ee.uct.ac.za |

|

AREA: |

Programmable logic, radar |

|

ID: |

MI-5 |

|

TITLE: |

GOTO Pedestal Software for NetRAD |

|

DESCRIPTION: |

The UCL/UCL NetRad S Band radar requires an antenna that can be pointed to ground geographic coordinates to high precision. The idea is to convert an amateur astronomy pedestal with motor control and “GoTo” interface to implement this functionality. For example, a boat with a GPS will telemeter its GPS coordinates to the pedestal, and the pedestal will then be required to track the vessel. We have a Mead LX80 pedestal and interface hardware / software. |

|

DELIVERABLES: |

Working software with suitable control interface. |

|

SKILLS/REQUIREMENTS: |

Reasonable coding skills (probably Python). |

|

EXTRA INFORMATION: |

|

|

AREA: |

Mechatronics or ECE |

|

ID: |

MI-6 |

|

TITLE: |

EW pedestral conversion |

|

DESCRIPTION: |

We have a number of ex SA Navy jammer pedestals, which use synchro transmitters to measure azimuth and elevation pointing of the antennas. We wish to replace these angle readouts with digital shaft encoders. There is scope to then place the pedestals under computer control. |

|

DELIVERABLES: |

Converted pedestal and measurements of angular precision. |

|

SKILLS/REQUIREMENTS: |

Mechanical ability, and some electrical interfacing skills. |

|

EXTRA INFORMATION: |

|

|

AREA: |

Mechatronics |

|

ID: |

MI-7 |

|

TITLE: |

Analysis of target backscatter measurements |

|

DESCRIPTION: |

We have 2-18GHz swept frequency measurements of spherical targets of various diameters taken in an anechoic chamber at Sydney University. We wish to calibrate these measurements and demonstrate the Mie scattering phenomenon. Calibration is usually by using one size sphere’s response and its known scattering properties to remove measurement system imperfections, background scattering. |

|

DELIVERABLES: |

Report detailing the method used to calibrate the measurements and correlation with theory. |

|

SKILLS/REQUIREMENTS: |

Coding skills and knowledge of RF scattering |

|

EXTRA INFORMATION: |

|

|

AREA: |

RF, Signal and image processing |

|

ID: |

MI-8 |

|

TITLE: |

Radar signal processing on Rhino board |

|

DESCRIPTION: |

Rhino board is a UCT endeavor and has a powerful FPGA and other peripherals on it. This project will aim at porting signal processing algorithms onto Rhino using an in-house developed flow. |

|

DELIVERABLES: |

Signal processing algorithm implemented on FPGA |

|

SKILLS/REQUIREMENTS: |

Coding skills: VHDL, Python and Matlab |

|

EXTRA INFORMATION: |

|

|

AREA: |

VLSI-DSP |

|

ID: |

MI-9 AMI & MI |

|

TITLE: |

Forward-looking radar for a small satellite |

|

DESCRIPTION: |

South Africa is planning to launch its first ARMC satellite within next 4-5 years. An useful addition to the payload of the satellite will be a radar system. However, because of constraints of a small satellite, we need to think of innovative ways.

This project will involve the study and feasibility analysis for a Forward-looking Radar for a small satellite. |

|

DELIVERABLES: |

Feasibility analysis of Forward-looking Radar |

|

SKILLS/REQUIREMENTS: |

|

|

EXTRA INFORMATION: |

http://ieeexplore.ieee.org/xpls/abs_all.jsp?arnumber=5758896 http://ieeexplore.ieee.org/xpls/abs_all.jsp?arnumber=5723693 |

|

AREA: |

ECE, Mechatronics |

Topics Proposed by R. Geschke

Email: Riana.Geschke[at]uct.ac.za

RHG-1: Antenna with Reconfigurable Radiation Pattern for Wireless Sensor Networks

Prerequisites: EEE4088

It will be required to master the basics of antenna design and the basics of applied computational electromagnetics as necessary to use the software FEKO correctly and optimally.

Description: This project aim is to provide an antenna operating within a 2.4 GHz wireless sensing network to enable communication between nodes. It is intended for predator tracking and associated environmental monitoring between nodes in an ad-‐hoc sensing network in the Northern Cape. The intention is to establish the best communications link budget to other nodes in the vicinity, by sequential sector selection. The selected sector covered by each node’s antenna will be dynamically adjusted, or switched, to continually optimize signal quality.

A suitable antenna topology should be chosen, using a single fed antenna element and various parasitic elements de/activated by switches. Its operation should include electronic selection of five different radiation patterns: either focused in one of four quadrants or an H-‐plane omnidirectional pattern. A design procedure will be established that includes the antenna topology and design, the use of PIN diodes and the required DC biasing. The antenna will be manufactured and its performance evaluated. This project focuses entirely on the antenna design, while the selection algorithm is excluded from the scope of this work.

Deliverables:

· A project report, detailing the theoretical background, antenna design, simulation, final layout, measurement results and critical evaluation of the designed antenna performance as compared to specifications. The report should be accompanied by all design and simulation files relating to the antenna design and the final layout files as submitted for manufacturing.

· A prototype antenna meeting the project specifications.

RHG-2: Antenna with Tunable Reflector Surface for Predator Tracking by Wireless Sensor Networks

Prerequisites: EEE4088

It will be required to master the basics of antenna design and the basics of applied computational electromagnetics as necessary to use the software FEKO correctly and optimally.

Description: This project aims to provide an antenna operating within a 2.4 GHz wireless sensing network to enable communication between nodes. It is intended for predator tracking and associated environmental monitoring between nodes in an ad-‐hoc sensing network in the Northern Cape. The intention is to establish the best communications link budget to other nodes in the vicinity. The selected sector covered by each node’s antenna would be dynamically adjusted to continually optimize signal quality in the particular internode direction.

For the project, a suitable antenna topology should be identified, including electronic tuning capabilities to steer the direction of the main antenna beam. Specifically, the design should include an electronically reconfigured reflector surface consisting of resonant elements activated or deactivated by diodes. The design includes all aspects of the reflector grid configuration, the biasing of the diodes connecting the grid elements and also the main antenna design. This project focuses entirely on the antenna design, while the selection algorithm is excluded from the scope of this work.

Deliverables:

· A project report, detailing the theoretical background, antenna design, simulation, final layout, measurement results and critical evaluation of the designed antenna performance as compared to specifications. The report should be accompanied by all design and simulation files relating to the antenna design and the final layout files as submitted for manufacturing.

· A prototype antenna meeting the project specifications.

RHG-3: Antenna for Predator Tracking Collar

Prerequisites: EEE4088

It will be required to master the basics of antenna design and the basics of applied computational electromagnetics as necessary to use the software FEKO correctly and optimally.

Description: This project involves the design and testing of an antenna embedded into a tracking collar, for wildlife management and research. The antenna must fit into a collar of approximately 130-150 mm diameter, which is to be fitted around the animal's neck. The target animal is a leopard or a jackal. The operating frequency is either 152 or 433 MHz. Modelling using FEKO is required, and the constructed prototype should be tested by a measurement procedure aiming to recreate a realistic operating environment.

Deliverables:

· A project report, detailing the theoretical background, antenna design, simulation, final layout, measurement results and critical evaluation of the designed antenna performance as compared to specifications. The report should be accompanied by all design and simulation files relating to the antenna design and the final layout files as submitted for manufacturing.

· A prototype antenna meeting the project specifications.

RHG-4: X-band Antenna for Drone Project

Prerequisites: EEE4088

It will be required to master the basics of antenna design and the basics of applied computational electromagnetics as necessary to use the software FEKO correctly and optimally.

Description: This project links into the drone project led by Dr Amit Mishra. (Refer to his project descriptions for more details). A communication link will be established at X-band, for which a suitable antenna is required. The project requires the selection of an antenna configuration determined by the system specifications. This will be followed by the design and computer simulation phase and subsequently the manufacturing and measurement of the final antenna.

Deliverables:

· A project report, detailing the theoretical background, antenna design, simulation, final layout, measurement results and critical evaluation of the designed antenna performance as compared to specifications. The report should be accompanied by all design and simulation files relating to the antenna design and the final layout files as submitted for manufacturing.

· An antenna suitable and ready for integration.

RHG-5: X-band Substrate-integrated Waveguide (SIW) Filter for Drone Project

Prerequisites: EEE3055

It will be required to master the basics of filter design, the basics of applied computational electromagnetics as necessary to use the software Sonnet, and establishing a design procedure.

Description: This project links into the drone project led by Dr Amit Mishra. (Refer to his project descriptions for more details on the drone project). A communication link will be established at X-band for which an X-band filter will be required (see project RHG-1).

Waveguide filters are commonly used in applications where low-‐losses are required. These filters may be large and heavy, especially at lower frequencies and require specialized manufacturing. A simplified version of waveguide or cavity filters may be implemented using microstrip technology. The metallic sidewalls of conventional waveguides are replaced by metallic vias or posts, positioned at regular intervals. These extend between the top and bottom side surfaces of the structure. While not all the advantages of conventional waveguide filters are retained, these Substrate-‐integrated-‐waveguide filters (SIW) filters are inexpensive to manufacture and have less losses than microstrip filters. A previous project established the basics of design, but the filter construction was complicated by the required metallic enclosure. The new filter design should not require the filter to be enclosed by a metallic box and design should keep the manufacturability of the filter in mind from the start.

Deliverables:

· A project report, detailing the theoretical background and design of the filter. The report should be accompanied by all design and simulation files relating to the design and the final layout files as submitted for manufacturing.

· A prototype filter.

RHG-6: Quasi-lumped Element Microwave Filter Design for Multilayer Layouts

Prerequisites: EEE3055 or EEE4088

It will be required to master the basics of filter design and applied computational electromagnetics as necessary for the software FEKO and Sonnet.

Description: This project investigates the implementation of quasi-lumped elements on multilayer LCP substrates. Inductors and capacitors in circuit models are replaced by multilayer structures representing these ideal elements over the frequency band of use. Parameter extraction, design procedure and efficient modelling using Microwave Office and FEKO will be investigated. A narrow-band filter operating at 2.4 GHz will be designed as proof of concept.

Deliverables:

A project report, detailing the theoretical background and detail relevant to the realization of quasi-lumped elements and the design of the filter. The report should be accompanied by all design and simulation files related to the project.

RHG-7: Quasi-lumped Element Directional Coupler Design for Multilayer Layouts

Prerequisites: EEE3055 or EEE4088

It will be required to master the basics of design and applied computational electromagnetics as necessary for the software FEKO and Sonnet.

Description: This project investigates the implementation of quasi-lumped elements on multilayer LCP substrates. Inductors and capacitors in circuit models are replaced by multilayer structures representing these ideal elements over the frequency band of use. Parameter extraction, design procedure and efficient modelling using Microwave Office and FEKO will be investigated. A directional coupler operating between 2.4 and 2.5 GHz will be designed as proof of concept.

Deliverables:

A project report, detailing the theoretical background and detail relevant to the realization of quasi-lumped elements and the design of the filter. The report should be accompanied by all design and simulation files related to the project.

RHG-8: Quasi-lumped Element Dual-band Filter Design for Multilayer Layouts

Prerequisites: EEE3055 or EEE4088

It will be required to master the basics of design and applied computational electromagnetics as necessary for the software FEKO and Sonnet.

Description: This project investigates the implementation of quasi-lumped elements on multilayer LCP substrates. Inductors and capacitors in circuit models are replaced by multilayer structures representing these ideal elements over the frequency band of use. Parameter extraction, design procedure and efficient modelling using Microwave Office and FEKO will be investigated. A dual-band filter with passbands at 2.4 and 3.5 GHz will be designed as proof of concept.

Deliverables:

A project report, detailing the theoretical background and detail relevant to the realization of quasi-lumped elements and the design of the filter. The report should be accompanied by all design and simulation files related to the project.

Topics Proposed by A. Mishra

|

ID: |

AMI-1 |

|

TITLE: |

Doppler Radar based Human Gait |

|

DESCRIPTION: |

Human motion or gait has been shown to have distinctive signature for different persons. Human gait recognition using optical sensors has been an emerging research area. This project will involve building a Doppler based motion sensor Radar using a pre-packed RF module, taking measurements, and analysing the measured signal to characterise human gait based signatures. A close work can be found at: http://www.mitre.org/work/tech_papers/tech_papers_05/05_0330/05_0330.pdf |

|

DELIVERABLES: |

Gait recognition setup |

|

SKILLS/REQUIREMENTS: |

coding skills (preferably in a scripting language like Python); understanding of electromagnetic scattering |

|

EXTRA INFORMATION: |

http://www.mitre.org/work/tech_papers/tech_papers_05/05_0330/05_0330.pdf |

|

AREA: |

Radar, signal processing |

|

ID: |

AMI-2 |

|

TITLE: |

Compressive Sampling for SAR Imaging |

|

DESCRIPTION: |

Compressive sampling (CS) is a very new way of looking at the fundamental DSP block of signal sampling. In CS we sample at a rate much lower than that required by Nyquist rate and using convex optimization try to reconstruct the desired image. CS has been used in Radar imaging in some works in last few years. In the current work, the student will use different convex optimization algorithms to find the best CS-algorithm for Radar imaging purpose. |

|

DELIVERABLES: |

Algorithms to frame Radar images using less amount of samples |

|

SKILLS/REQUIREMENTS: |

Coding skills in Matlab/Octave and understanding of linear algebra |

|

EXTRA INFORMATION: |

http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=5712730 |

|

AREA: |

Signal processing. |

|

ID: |

AMI-3 |

|

TITLE: |

Cognitive Architecture on FPGA |

|

DESCRIPTION: |

There have been quite a few architectures proposed to emulate the function of brain. This project will aim to implement one of them on a general purpose FPGA board. |

|

DELIVERABLES: |

implementation on FPGA |

|

SKILLS/REQUIREMENTS: |

VHDL/Verilog, Java, computer architecture |

|

EXTRA INFORMATION: |

|

|

AREA: |

Computer science |

|

ID: |

AMI-4 |

|

TITLE: |

FM tuner for Smart-phone |

|

DESCRIPTION: |

During peak periods, most FM stations air music only 30-40% of the time. This project will aim to develop an app which will try to sample the signal and if the signal changes from music to talk, it will automatically find another station which is airing music of the same genre that the previous station was transmitting. |

|

DELIVERABLES: |

Application written in Java |

|

SKILLS/REQUIREMENTS: |

Java programming skills and android app. development skills |

|

EXTRA INFORMATION: |

http://developer.android.com/index.html |

|

AREA: |

Signal processing, pattern recognition, computer science |

|

ID: |

AMI-5 |

|

TITLE: |

Evolutionary algorithms to design the placement of SKA antennas |

|

DESCRIPTION: |

The Square Kilometer Array (SKA) project is one of the biggest science project of this century and South Afirca is proud to be a major site where these antennas will be placed. One of the non-trivial questions for SKA is the arrangement of antennas. The total number of antennas to be placed will be around 3000. And there are many engineering constrants. This makes it a classic multi-objective optimization problem. In this project the student will develop an evolutionary algorithm (e.g. genetic algorithm, ant colony optimization etc. ) to solve this problem. |

|

DELIVERABLES: |

Placement plan for 3000 antennas in SKA |

|

SKILLS/REQUIREMENTS: |

|

|

EXTRA INFORMATION: |

http://www.skatelescope.org/the-location/layout/ |

|

AREA: |

ECE, Mechatronics |

|

ID: |

AMI-6 |

|

TITLE: |

Error analysis of SKA Digital Backend (DBE) |

|

DESCRIPTION: |

The Square Kilometer Array (SKA) project is one of the biggest science project of this century and South Afirca is proud to be a major site where these antennas will be placed.

Digital back-end of these antennas will be complex high performance computing platforms, mostly to be implemented using GPUs or FPGAs. Each system design involves many parameters which most of the times affect the performance of the system in a non-linear way. A mathematical model desribing how the choice of different parameters affect the final performance in terms of extra noise, is a crucial contribution.

In this project, the student will study the digital back end of SKA antennas, and make models to predict the SNR of the system for a certain choice of design parameters. |

|

DELIVERABLES: |

madel and codes to determine the SNR for different choices of parameters |

|

SKILLS/REQUIREMENTS: |

engineering modelling, numerical analysis |

|

EXTRA INFORMATION: |

|

|

AREA: |

ECE, EE, Mechatronics |

|

ID: |

AMI-7 |

|

TITLE: |

Drone-SAR Design |

|

DESCRIPTION: |

The use of flying radio sensors is crucial for a number of applications starting from disaster management to drug control. The recent issue in IEEE Proceedings ran a special issue[1] on the use of Radar based remote sensing for disaster management. Radar Remote Sensing Group of UCT has a rich experience of developing synthetic aperture radar[2] and is one of the first academic groups in the world to develop one. The group also has a lot of expertise in developing digital backend for Radars[3]. Lastly there has been a lot of development in the field of open source designs for building drones. E.g. www.diydrones.com which is an open source initiative that has completely disrupted commercial drone technology for aerial photography by providing a low cost alternative to fully automated and stable flight platform.

This project will be on the top level design analysis for the system.

[1] http://ieeexplore.ieee.org/xpl/tocresult.jsp?isnumber=6303861&punumber=5 [2] M.R. Inggs, ``The SASAR VHF Sensor,'' Proc. European Conference on Synthetic Aperture Radar, EUSAR'96, Königswinter, Germany, pp. 317-320, March 1996. [3] Raw B, Winberg S, and Mishra AK, “Rhino Blocks Pulse-Doppler Radar Framework”, 2nd IEEE International Conference on Parallel, Distributed and Grid Computing, December 2012.

|

|

DELIVERABLES: |

Design recommendations which will include recommendation for a specific drone, power system, power source, telemetry options and digital backend options. |

|

SKILLS/REQUIREMENTS: |

System design |

|

EXTRA INFORMATION: |

|

|

AREA: |

mechatronics |

|

ID: |

AMI-8 |

|

TITLE: |

OFDM radar data processing |

|

DESCRIPTION: |

The emergence of new digital technologies,

and the growing constraints on the RF spectrum In the current work, the student will be

given a set of raw data recorded with a prototype

General signal processing techniques include |

|

DELIVERABLES: |

Matlab scripts, Range / Doppler map of

scenarios of interest, light report focused on |

|

SKILLS/REQUIREMENTS: |

Coding skills in Matlab, understanding of Time/Frequency analyses, curiosity in radar. |

|

EXTRA INFORMATION: |

|

|

AREA: |

Signal processing. |

|

ID: |

AMI-9 |

|

TITLE: |

The effect of nonlinear windowing on practical signal processing |

|

DESCRIPTION: |

Sidelobes are known to have reduced the quality of any coherent imaging system including Radar images. One of the new generation tools to get rid of side-lobes is non-linear apodization or nonlinear filtering. This project will involve the study of the effect of nonlinear filtering on real life signal processing (e.g. speech, image or radar signal processing chain). |

|

DELIVERABLES: |

Algorithms to supress sidelobes in Radar images |

|

SKILLS/REQUIREMENTS: |

Coding skills in Matlab and basic signal processing knowledge |

|

EXTRA INFORMATION: |

http://ieeexplore.ieee.org/assets/img/btn.pdf-access-full-text.gif |

|

AREA: |

signal processing |

|

ID: |

AMI-10 |

|

TITLE: |

Frequency domain Radar based target recognition |

|

DESCRIPTION: |

Radar based target recognition is one of the major uses of Radar systems. With current trend towards building wide-band Radars, there is a need to analyse the possibility of recognizing the targets in frequency domain. This project will aim at analysing the RF return from basic shapes like spheres and extracting recognition-worthy features from the same. |

|

DELIVERABLES: |

Features in frequency domain which can be used to recognize targets |

|

SKILLS/REQUIREMENTS: |

Coding skills and knowledge of RF scattering |

|

EXTRA INFORMATION: |

http://www.eurasip.org/Proceedings/Eusipco/Eusipco2011/papers/1569432321.pdf |

|

AREA: |

Signal and image processing |

|

ID: |

AMI-11 |

|

TITLE: |

Low cost ECG using android phone |

|

DESCRIPTION: |

ECG is a crucial biological signal. This project aims at developing an ECG monitoring system centered around an android phone. |

|

DELIVERABLES: |

Working ECG monitor |

|

SKILLS/REQUIREMENTS: |

Analog hardware design & android app. development skills |

|

EXTRA INFORMATION: |

|

|

AREA: |

Embedded systems |

|

ID: |

AMI-12 |

|

TITLE: |

Cognitive recognition based on brain architecture |

|

DESCRIPTION: |

Cognitive engineering is a subject which has got some renewed interest of late. This project will look into exploiting some of the existing systems emulating human brain for the purpose of pattern classification. |

|

DELIVERABLES: |

Pattern classification algorithm using brain architecture |

|

SKILLS/REQUIREMENTS: |

Coding skills: C++, Matlab/Octave |

|

EXTRA INFORMATION: |

|

|

AREA: |

Machine learning |

|

ID: |

AMI-13 |

|

TITLE: |

Information geometry based target recognition |

|

DESCRIPTION: |

Radar based target recognition is an ongoing active field for research and development. This project will aim at the use of information geometry based approaches to classify targets from radar images. |

|

DELIVERABLES: |

target recognition scheme using information geometry |

|

SKILLS/REQUIREMENTS: |

Coding skills: Matlab/Octave |

|

EXTRA INFORMATION: |

http://ieeexplore.ieee.org/xpls/abs_all.jsp?arnumber=6139379&tag=1 |

|

AREA: |

Machine learning |

|

ID: |

AMI-14 |

|

TITLE: |

MIMO Radar Imaging |

|

DESCRIPTION: |

Imaging using multiple transmitters and multiple receivers is a non-trivial task. This project will involve the development of a scheme to optimally image using multiple Tx and multiple Rx. |

|

DELIVERABLES: |

Validation of certain radar imaging algorithms. |

|

SKILLS/REQUIREMENTS: |

Coding skills: Matlab/Octave |

|

EXTRA INFORMATION: |

V. K. Ithapu, A. K. Mishra, Cooperative MultiMonostatic SAR: A New SAR Configuration for Improved Resolution, IEEE Antennas and Wireless Propagation Letters. |

|

AREA: |

Signal processing |

Topics Proposed by A. Van Der Byl

Email: a.vanderbyl[at]uct.ac.za

|

ID: |

AVDB-1 |

|

TITLE: |

Simple ADC and DAC Interface for Rhino |

|

DESCRIPTION: |

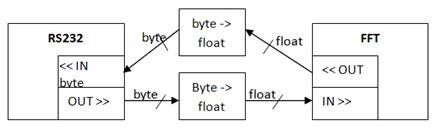

The Rhino board has an on-board stereo audio codec interfaced with the microprocessor. The aim of the project is to write an interface to access data from the ADC for signal acquisition, and send data to the DAC for signal synthesis. The student should demonstrate correct signal acquisition through the use of FFT libraries executed on the microprocessor. |

|

DELIVERABLES: |

Report describing results of experiments |

|

SKILLS/REQUIREMENTS: |

Programming in a languages such as Python. |

|

EXTRA INFORMATION: |

No hardware will be needed

to be built. The Rhino s already equipped with the codec hardware. |

|

AREA: |

Software Defined Radio |

|

ID: |

AVDB-2 |

|

TITLE: |

Video Interface for Rhino |

|

DESCRIPTION: |

The Rhino board has an on-board video rendering capability. The aim of the project is to write an interface to display data visually through the HDMI interface. |

|

DELIVERABLES: |

Report describing results of experiments |

|

SKILLS/REQUIREMENTS: |

Programming in a languages such as Python. |

|

EXTRA INFORMATION: |

No hardware will be needed

to be built. The Rhino s already equipped with the hardware. |

|

AREA: |

Software Defined Radio |

|

ID: |

AVDB-3 |

|

TITLE: |

DSP on Rhino |

|

DESCRIPTION: |

The Rhino board has both an FPGA and a Microprocessor which is equipped with an on-chip SIMD co-processor (NEON). The aim of the project is to write an interface to access the processing capability of the NEON co-processor. The student should be able to benchmark the performance and run typical DSP algorithms such as the FFT. |

|

DELIVERABLES: |

Report describing results of experiments |

|

SKILLS/REQUIREMENTS: |

Programming in a languages such as Python. |

|

EXTRA INFORMATION: |

No hardware will be needed

to be built. The Rhino s already equipped with the hardware. |

|

AREA: |

Software Defined Radio |

|

ID: |

AVDB-4 |

|

TITLE: |

Low-Cost Power Monitor |

|

DESCRIPTION: |

Energy is an important resource that should be used conservatively. Most home users are not aware of the demand certain appliances place on the grid. The purpose of this project is to build a small low-power energy meter which can be fitted into a multiway plug extension with either an LCD or LED display. |

|

DELIVERABLES: |

Artifact and report describing results of experiments |

|

SKILLS/REQUIREMENTS: |

Programming in a languages such as C or Python. PCB layout and hardware design. |

|

EXTRA INFORMATION: |

There are specific Texas Instruments microprocessors designed for this purpose (which we have). This will be made available to the student during development. |

|

AREA: |

Power Conservation. This topic is open to EE, EC and Mechatronics students. |

Topics proposed by S. Winberg

CATEGORY: EMBEDDED SYSTEMS & SIGNAL PROCESSING

|

ID: |

SW-1 |

|

|

TITLE: |

UTED – Ultrasonic Trajectory Estimation Device(a signal processing theme) |

|

|

DESCRIPTION: |

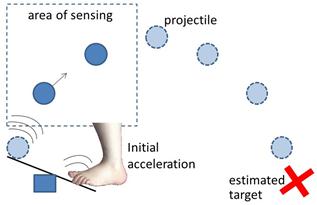

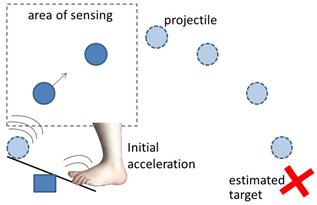

The UTED is a device used for measuring the speed, size and launch velocity of a projectile, and to gauge its final endpoint. The diagram below illustrates the problem. There is certain amount of flexibility, and scalability of scope, for this project.

|

|

|

DELIVERABLES: |

Operational prototype assembled using either combination of evaluation board and veriboard circuit, or a prototype pcb of your own design. Adequate GUI to display results. |

|

|

SKILLS/REQUIREMENTS: |

Signal processing, Electronics, Microcontroller programming, C programming |

|

|

EXTRA INFORMATION: |

|

|

|

AREA: |

Embedded Systems, Signal processing, C/C++ programming |

|

|

ID: |

SW-2Supervisors: S. Winberg & G. De Jager |

|

TITLE: |

RPSFSS – Raspberry Pi Sensor Fusion Security System |

|

DESCRIPTION: |

The Raspberry Pi is a low cost ARM-based single board computer system that is well supported by the Linux operating system. The platform provides a variety of useful ports, such as HDMI graphics, USB and Ethernet. The objective of this project is to create an ‘intelligent’ security system using the Raspberry Pi. The project is to contribute artificial intelligence / machine learning code and experimental findings, also application code, to the Raspberry PI interest group (see site at: http://www.dovgalecs.com/Vlads_spot/Raspberry_Pi.html). The student doing this project is encouraged to contact this interest group, tell them about the project, become familiar with their mission plans, and obtain and build on any existing support code they have.

Figure: Raspberry Pi platform For this project, standard off-the-shelf webcams should be used for surveillance, intruder detection and system activation/deactivation. If time permits, acoustic detection and alarm triggering will be added, constituting a sensor fusion aspect to this project as a means to validate alarm conditions and authorization for configuration changes. Further info related to the design tasks: A suitable enclosure needs to be built. The alarm system can be powered via mains using a standard USB cellphone charger. Audio input can be provided via a microphone circuit to the analogue in GPIO line. The system should work on a home network; an Ethernet to Wifi switch can be provided to connect to a home wireless Wifi network. A web-based interface to the system needs to be implemented for configuration, to activate/deactivate alarms, and to check alarm conditions. Email messages for alarm should also be provided. It is the student’s responsibility to come up with creative approaches to implement the system and sensor fusion techniques. |

|

DELIVERABLES: |

Raspberry PI integrated into a suitable enclosure Completed security system with suitable testing environment Security software, User manual |

|

SKILLS/REQUIREMENTS: |

Programming; Embedded systems. |

|

EXTRA INFORMATION: |

See the Raspberry Pi website at: http://www.raspberrypi.org/ |

|

AREA: |

Computer Engineering / Mechatronics (provided student has good programming ability) |

|

ID: |

SW-3 |

|

|

TITLE: |

RMB - Retro Morsecode Box(a music theme project) |

|

|

DESCRIPTION: |

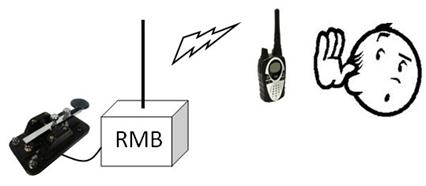

This is another one for those interested in music, but for also for people with an appreciation for history and classic electronics. You certainly don't need to be good at music for this project. The aim of the Retro Morsecode Box (or RMB) is to revisit the exciting bygone erra of mosecode and telegraphs. You have an option of either creating a wireless morse code device, which you can use a walkie-talkie (or appropriately configured radio received) to listen to your beep boop tunes. Alternatively, you can develop a wired system to listen to your RMB transmissions, in which case you'll probably need to create a prototype PCB (e.g. using breadboards or veriboard), one for sending and the other for receiving (you don't need to do two-way comms). You'll need to do some tests to see what kind of distance you can get, how well the signals can travel through walls, etc. If you want to take it further you can hook up PCs to control the sending and receiving of data as Morse code (i.e., replacing the human operator by a machine). The diagram below suggests what is needed.

|

|

|

DELIVERABLES: |

Prototyped RMB device. Demonstrate sending and receiving of morsecode signals. Report on distance tests (part of thesis). |

|

|

SKILLS/REQUIREMENTS: |

Electronics, microcontroller programming, C programming |

|

|

EXTRA INFORMATION: |

|

|

|

AREA: |

Electronics, Embedded systems |

|

|

ID: |

SW-4 |

|

|

TITLE: |

RWTM - Rhino Wireless

Transceiver Module |

|

|

DESCRIPTION: |

The Rhino project is a reconfigurable computing platform designed

for Software Defined Radio (SDR) applications. The Rhino platform was built

at UCT by the SDRG research group (see the www.rhinoplatform.org Rhino site for

details). |

|

|

DELIVERABLES: |

Prototyped antenna and analogue front-end (which connects to a A2D sampling module), VHDL/Verilog code for the front-end processing and Wireless communications protocol handling. |

|

|

SKILLS/REQUIREMENTS: |

Embedded systems; HDL coding; digital single processing; a reasonable understanding of signals and RF transmissions (although much of the RF skills you can pick up as part of doing this project) |

|

|

EXTRA INFORMATION: |

|

|

|

AREA: |

Digital systems; Electronics |

|

|

ID: |

SW-5 |

|

|

TITLE: |

SwaMURAy – Swapping

Memory Unit for Radio Astronomy (a

Reconfigurable Computing theme project) |

|

|

DESCRIPTION: |

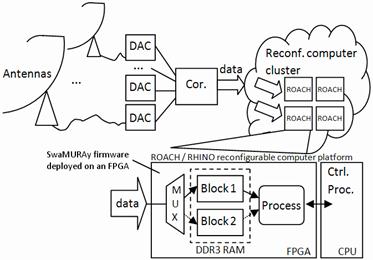

This project focuses on developing a portable signal processing firmware service useful for Radio Astronomy (RA) processing purposes. RA usually needs to deal with big data volumes, what have usually been pre-correlated as shown in the figure below. A cluster of reconfigurable computing platforms can be an effective means to deal with large volumes of data by doing special-purpose processing on it in parallel at high speed. This is the case for many radio astronomy data processing centres, including the one for the South African Square Kilometre Array (SKA).

Figure: How the SwaMURAy module fits in A common method for RA signal processing application involves the simultaneous, or overlapping, acquisition of data and processing of previously acquired signals. Essentially, this involves two (or more) blocks of memory. Digitized signals from an ADC (or network) is saved to the first block. When the block is full, processing is applied to this block (e.g. an FFT) and the data being received is switched to writing to the second block. Similarly, when the second block is full, processing is applied to it which data reverts to being written to the first block and so on.

This project has the following objectives: 1) implement code to read and write to DDR3 memory on ROACH/Rhino; 2) develop simultaneous sampling and memory swapping scheme; and 3) determine the speed that HDL-based Fourier transforms can be done and the resultant transform produced while overlapped with the sampling operation.

Students doing this project may need to have occasionally meetings at the SKA office in Pinelands in order to refine the specifications, obtain sample code and data, and to show & discuss progress.

What is ROACH and what is Rhino? The ROACH platform (see: https://casper.berkeley.edu/wiki/ROACH) is a reconfigurable computing platform used in many radio astronomy data processing centres. The Rhino platform (www.rhinoplatform.org) is a lower cost reconfigurable platform intended as a training platform for RA processing and to facilitate progression towards use of ROACH. Rhino can serve as an alternate platform for RA applications. |

|

|

DELIVERABLES: |

1. Well document code modules for: a) DDR3 memory access; b) memory swapping control; c) FFT processing operation. 2. Prototyped processing system running on either ROACH or Rhino. |

|

|

SKILLS/ REQUIREMENTS: |

Embedded systems; HDL coding; digital single processing. |

|

|

EXTRA INFORMATION: |

|

|

|

AREA: |

Computer engineering / Digital systems |

|

|

ID: |

SW-6 |

|

|

TITLE: |

PRTF - Populating the Rhino Toolflow Framework |

|

|

DESCRIPTION: |

The Rhino toolflow describes the development process

by which a design for signal processing operations is transformed through a

sequece of engineering tasks into an executable implementation that runs on

the Rhino. It is envisioned that that the framework designed will be

populated with common signal processing components such as filters, mixers,

signal sources etc, all of which are fairly primitive building-block

structures used in most signal processing operations. Consequently, this

project is concerned with the creation of a subset of these components, and

implementing and testing these on a Rhino board (or compatable FPGA

platform). These signal processing routes could be written in MyHDL or VHDL /

Verilog. Suitable documentation and integration procedures will need to be

defined and explained in the thesis. Acknowledgement: Thanks to Gordon Inggs for suggesting this idea. |

|

|

DELIVERABLES: |

toolset of signal processing routines written in an HDL |

|

|

SKILLS/REQUIREMENTS: |

FPGA application development, HDL coding |

|

|

EXTRA INFORMATION: |

|

|

|

AREA: |

Digital systems, FPGAs |

|

|

ID: |

SW-7 |

|

|

TITLE: |

mVAIS – Vision-based Alignment and Image transfer System (An image processing theme) |

|

|

DESCRIPTION: |

This project is done in collaboration with EDH Sports, a company that has an engineering division in Stellenbosch’s Technopark. In brief, this project involves writing embedded code, which will run on a platform developed by EDH, and will interface to an Omnivision high-performance camera (OV5640). The code needs to stream video to a host computer, and a special-purpose visual-based alignment algorithm needs to be implemented on the PC (once the streaming is working) and then tested comprehensively. The embedded platform comprises a special-purpose ARM processor (developed by Variscite http://www.variscite.com/). For this development work, the prototyping module VAR-SOM-OM44 illustrated below will be used. The module has a CPI interface to the OV5640 5Mp camera.

There will be support available from EDH, both in terms of in-person meetings and email, also trialling/demoing solutions at their labs with an industry expert to proffer advice. |

|

|

DELIVERABLES: |

Operational streaming of video from the OV5640 via the ARM to a PC host application. Operational alignment program running on host computer. Code repository, with neatly documented code |

|

|

SKILLS/REQUIREMENTS: |

Hardware/Software interfacing. Understanding of signal processing techniques. Numerical methods. |

|

|

EXTRA INFORMATION: |

|

|

|

AREA: |

Computer engineering. Signal proc., networks (sockets), embedded s/w |

|

|

ID: |

SW-8

|

|

|

TITLE: |

Porting of the Commensal Radar Processing Server from a CUDA implementation to standard multi-threaded CPU implementation (image processing theme) |

|

|

DESCRIPTION: |

The UCT Commensal Radar (CR) project (http://www.cr.uct.ac.za) currently makes use of a CUDA-accelerated processing server application to perform the signal-processing necessary to detect aircraft. The aim of this project is to port the CUDA portions of the server code to standard CPU code to run on a typical desktop or laptop processor to allow processing of data when a GP-GPU device is not available.

A module diagram of the processing server is shown below. The student is required to re-write the Processing module. This block consists of several calls to CUDA-BLAS routines as well as some hand-written arithmetic routines. These need be changed to CPU implementations of BLAS and/or hand-written routines. There is plenty of real radar data available to test the implementation as well as several multicore hardware platforms. |

|

|

|

||

|

DELIVERABLES: |

Operational CPU / non-CUDA implementation of the CR routine |

|

|

SKILLS/REQUIREMENTS: |

C++, Threaded programming, Cuda, Linux, matrix algebra, some basic knowledge of DSP. |

|

|

EXTRA INFORMATION: |

|

|

|

AREA: |

Computer engineering, algorithm development, Signal processing |

|

CATEGORY: IMAGE PROCESSING

|

ID: |

SW-9 |

|

|

TITLE: |

VTED – Visual Trajectory Estimation Device(an image processing theme) |

|

|

DESCRIPTION: |

The VTED is a device used for measuring the speed, size and launch velocity of a projectile, and to gauge its final endpoint. A nice thing about this project is that it aims to use a standard PC and (fast) webcam (i.e., a 40+ fps PlayStation eye webcam). The requirements for this project are largely the same as those for the ultrasonic-based UTED project above – but they two projects use extensively different signal processing operations (if someone else chooses SW-1, you are encouraged to collaborate with them, which the supervisor of this project will elaborate to ensure each project has the necessary substantive amount of individual work). Indeed, the point of advertising the two projects is to stimulate a bit of competition: will UTED work better than VTED?! The diagram below illustrates the trajectory problem. There is some flexibility and scalability of scope for this project.

The baseline system for this project planned around development and deployment on the same machine, a standard PC with a webcam attached. The projectiles will need to be sufficiently large and in order to work effectively with the camera system (the PS Eye is fast but quite low res). For example, launching a nice bright rubber ball from a simple catapult, with the particular weight and size of the ball know, can be used as an initial starting point to characterize the problem, which can be later expanded to incorporate other types of projectiles, such as darts, tennis balls, plastic bottles, beer bottles, stones, and a broader variety of other things. Also see: UTED above. |

|

|

DELIVERABLES: |

Software implementing VTED. Short manual explaining how to use it. |

|

|

SKILLS/REQUIREMENTS: |

Signal processing, C/C++ programming |

|

|

EXTRA INFORMATION: |

|

|

|

AREA: |

Electronics, Embedded systems |

|

|

ID: |

SW-10 |

|

|

TITLE: |

Golf Ball Launch Angle Calculator (GBLAC)(an image processing theme) |

|

|

DESCRIPTION: |

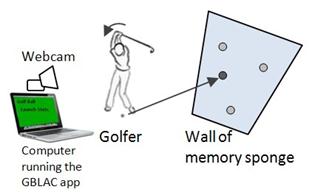

If you’re interested in golf, or in a sporting and peaceful equivalent of launching missiles, then this project is for you. The objective of this project is to calculate the launch angle of a golf ball by ‘seeing’ (from a camera) where it ends up in a wall coated with sponge memory foam. This project is done in collaboration with EDH Sport, a company that has a development division in the Stellenbsoch Technopark (see transport issues below). The system is intended to work as illustrated below. Essentially, a webcam continuously monitors the wall of memory foam. When a new hole appears in the wall (from a golf ball hitting it) the launch trajectory needs to be calculated (from the initial conditions that are to be configured via a GUI). Ideally, a sound trigger should be built into the system which starts the processing when the sound of the golf club hitting the ball is detected.

Transport concerns: Occasional meetings and experimentation with a good golfer will be necessary; it would therefore be an advantage to the student if he/she has a car; reimbursement of travel expenses to Technopark can be made. |

|

|

DELIVERABLES: |

Operational GBLAC software application with easy to use GUI Short user manual explaining how to use the program Code neatly arranged into a project archive on CD. |

|

|

SKILLS/REQUIREMENTS: |

Signal processing, C/C++ programming |

|

|

EXTRA INFORMATION: |

|

|

|

AREA: |

Programming, GUI, some device driver interfacing to use webcam |

|

|

ID: |

SW-11 |

|

|

TITLE: |

FLORA – Fynbos Leaf-based Online Recognition Application V.3 |

|

|

DESCRIPTION: |

This project relates to performing image-processing and communications. The proposed product involves two parts: a cellphone or digital camera, referred to as the Image Capture Device (ICD) and a central processing server (CPS). The ICD will acquire an image of a leaf from a Fynbos plant; this image will be sent to the CPS for identification. The CPS will then attempt to identify the leaf based on matching its colour and shape, among other techniques, to a database of leaf characteristics and patterns. If the CPS is able to perform a match, it will send back a match accuracy measure (a percentage value indicating how likely the match is), of no matches are found, the CPS will send back a message indicating that the plant was not found and that the image has been tagged for a human expert to attempt to determine what plant the image represents. In the prototype version of the FLID, the connection between ICD and CPS will require manual intervention, such as the users needing to download the image from cellphone/camera and manually loading the image into the CPS program to identify the image. Furthermore, the prototype will be configured and tested with a relatively small set of samples which can be easily found around campus. This project is most suited for a student who's willing to spend some time in the outdoors looking for, and photographing plant specimens. A certain amount of literature review will be needed to become familiar with commonly used image-processing techniques needed for pattern matching algorithms. Future work plans could include having a both the ICD and CPS running as a cellphone application so that the identification can be performed without the need for a communications link. A start has been made on FLORA, viewable at: http://forge.ee.uct.ac.za/flora/ If you choose to work on this project, you can take it further. |

|

|

DELIVERABLES: |

Application running on an embedded platform or on a mobile computer or on a smartphone |

|

|

SKILLS/REQUIREMENTS: |

C / C++ programming (some experience with image processing is recommended but not essential) |

|

|

EXTRA INFORMATION: |

|

|

|

AREA: |

Digital image processing, signal processing |

|

|

ID: |

SW-12 |

|

|

TITLE: |

Implementation of Numberplate Recognition on the Raspberry PI Architecture |

|

|

DESCRIPTION: |

The aim of this project is to prototype a low-cost real-time number-plate recognition system, on the Raspberry PI platform. The project will be built using custom C++ implementations and the OpenCV (Open Source Computer Vision) libraries.

The Raspberry PI is a credit card sized single board computer, originally designed for teaching computer science in schools, which has now been used in many applications in various sectors, from education to engineering to entertainment.

The board features a 700 MHz ARM based processor, 512MB ram, RCA and HDMI video output, 3.5mm sound output, two USB ports, an ethernet port, and a number of digital I/O pins. This low cost board can run ARM ported, heavily scaled linux distributions. |

|

|

DELIVERABLES: |

Prototype of number plate recognition running on the Raspberry Pi. Report documenting the methods used in this implementation, along with testing and analysis of system performance. |

|

|

SKILLS/REQUIREMENTS: |

Computer Science, C++, Embedded Systems, Engineering Design, GUI Design, Image Processing, Operating Systems |

|

|

EXTRA INFORMATION: |

Reserved for Steve Bissett See Also: · Engers, Ross - Realtime Optical Vehicle Entry/Exit Recognition: An application for vehicle numberplate recognition, University of Cape Town 2012 · Raspberry PI (Official Website): http://www.raspberrypi.org/ · OpenCV (Official Website): http://opencv.org/ |

|

|

AREA: |

Electrical and Computer Engineering, Embedded Systems, Computer Science, Operating Systems |

|

CATEGORY: MECHATRONICS

|

ID: |

SW-13 |

|

|

TITLE: |

O2LD3P – Open-source

& Open-plan Large-scale Dimensiones des 3 Printer (part A) |

|

|

DESCRIPTION: |

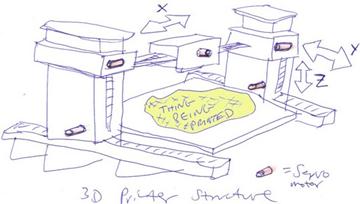

This project concerns the construction, development of driver code, and testing of a large-scale 3D printer system. This is a rather ambitious project, and we would need at least two students to work on it. There is plenty scope for multiple projects related to this, that is why there are two topic numbers allocated to this ‘meta-project’. The overall project has been divided into two parts: Part A is development of the physical printer system and its control electronics; Part B is development of the software control part and integration with a drawing program. Another, part, largely focused on programming, would need to be done for a Part C. This project is to be done in collaboration with DELtronics, who will fund the necessary parts and equipment and have also offered the availability of lab space needed to assemble the machine. Plans on what parts can be worked on where (i.e., on campus or at DELtronics) and transport issues would need to be negotiated with your supervisor and the DELtronics representative.

Figure: Rough diagram of how the printer might look The figure above suggests the printer structure. Further insights into how the printer and its control software is to be developed will need to be discussed in detail with the various parties concerned. |

|

|

DELIVERABLES: |

Prototyped 3D printer, demonstrating operation (done in conjunction with project partner) |

|

|

SKILLS/REQUIREMENTS: |

Mechanical design and construction; programming |

|

|

EXTRA INFORMATION: |

|

|

|

AREA: |

Mechatronics |

|

|

ID: |

SW-14 |

|

|

TITLE: |

O2LD3P – Open-source

& Open-plan Large-scale Dimensiones des 3 Printer (part B) |

|

|

DESCRIPTION: |

This project concerns the construction, development of driver code, and testing of a large-scale 3D printer system. See SW-11 for further detail on the overall project concern.

This part, Part B, focuses on development of the software control part of the O2LD3P project and integration with a drawing program. The code produced is intended to be made open-source and placed in a suitable repository on completion, such as sourceforge.net.

This project is to be done in collaboration with DELtronics. Plans on what parts can be worked on where (i.e., on campus or at DELtronics) and transport issues would need to be negotiated with your supervisor and the DELtronics representative. Further insights into this part of the project need to be discussed in detail with the various parties concerned. |

|

|

DELIVERABLES: |

Software for driving the prototyped 3D printer, demonstrating operation (done in conjunction with project partner) |

|

|

SKILLS/REQUIREMENTS: |

Programming / device driver coding; Mechatronics / control; |

|

|

EXTRA INFORMATION: |

|

|

|

AREA: |

Computer Engineering / Mechatronics |

|

|

ID: |

SW-15 |

|

|

TITLE: |

|

|

|

DESCRIPTION: |

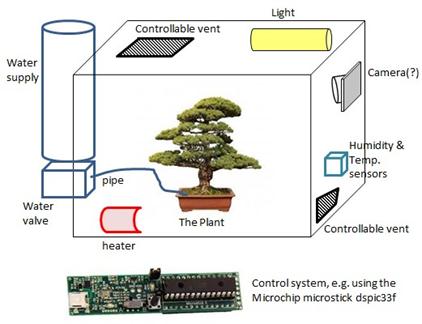

This project concerns the development of a miniature, environment controlled greenhouse. The system worked by opening/closing vents, activating/deactivating fats, turning on/off a mini heating device to swarm the enclosure. The control system can be implemented as a PC application that, e.g., controls the actuators and reads sensors via a parallel printer port (a USB to LPT printer interface is available for this purposes). The application also needs to log events and keep track of power usage (measuring power consumption doesn’t need to be done directly, it can be based on the amount of time spent activating a device and how long the heater was on for). This is a generally low-current system using max. 12V DC. See illustration below.

|

|

|

DELIVERABLES: |

Mini greenhouse structure. Control platform and control software. |

|

|

SKILLS/REQUIREMENTS: |

Programming, embedded systems. Mechanical construction. |

|

|

EXTRA INFORMATION: |

More info about planning & building a large scale greenhouse can be found at the following link, not all applies to a bonsai greenhouse: http://www.wvu.edu/~agexten/hortcult/greenhou/building.htm |

|

|

AREA: |

Mechatronics |

|

|

ID: |

SW-16 |

|

|

TITLE: |

WPGC – Wireless Pong Game Controlled

|

|

|

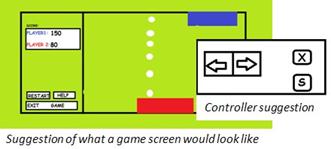

DESCRIPTION: |

This topic is based on developing two controllers that will be used to play the pinball game on the laptop. Both the controllers and a graphics game application need to be designed, implemented and tested. The suggested game is Pong, a game for which each player has a controllable paddle to defend their wall – if the ball hits a player’s wall, the other player wins a point. The program will interact with the controller via infrared connection to a COM port. The controller will have the following basic buttons shown below.

This project is intended to follow a research approach, in which a literature review will need to be done to decide methods to ergonomically design the controller, test the interfaces, perform surveys and the like in order to put together a topic quality report. |

|

|

DELIVERABLES: |

Pong controller, Pong game that works with the controller, Surveys completed by testers |

|

|

SKILLS/REQUIREMENTS: |

Mechanical design, Programming, Hardware/Software interfacing. |

|

|

EXTRA INFORMATION: |

Reserved for Mike Dlulane |

|

|

AREA: |

Mechatronics / computer engineering |

|

CATEGORY: HIGH PERFORMANCE COMPUTING & NETWORKING

|

ID: |

SW-17 |

||||||

|

TITLE: |

MDPN – Mobile Database POS Network System |

||||||

|

DESCRIPTION: |

Slave

Master WiFi / 3G Illustration of the MDPN System This system needs to have a well-defined interface (e.g. socket-based interface) so that it can be integrated quickly with other applications (e.g., GUIs) and remote database systems (e.g. for use with a security system or restaurant POS system). |

||||||

|

DELIVERABLES: |

Android executable program, Database, Subnet data transmission API, API Documentation, Thesis Document |

||||||

|

SKILLS/REQUIREMENTS: |

Java Programming, SQL, TCP/IP sockets programming |

||||||

|

EXTRA INFORMATION: |

Reserved for David Chaplin |

||||||

|

AREA: |

Networks, Network service programming, Mobile device programming, Database design |

|

ID: |

SW-18 |

|

|

TITLE: |

VTBA – Virtualization Technologies Benchmarking Analysis |

|

|

DESCRIPTION: |

This project concerns Virtualization Technologies, staring with a literature-based analysis of existing implementations. Building on this, the student is to determine the performance penalties associated with Virtualization over an unstructured cluster management approach by means of comparative benchmarking. The proposed hypothesis is that although overheads (e.g., hypervisors and network management) exist, their impact can be effectively minimized to the point where the administrative and management advantages of Virtualization outweigh the performance cost. The benchmarking process will be conducted on a HPC cluster in ACE Lab at the Centre for High Performance Computing (CHPC) Rosebank campus.

The testing process will be broken up as follows: 1. Produce a software stack for the HPC cluster. 2. Benchmark the cluster to ascertain a performance baseline. 3. Deploy an appropriate implementation of Virtualization Technology onto the cluster. 4. Reassess the performance of the cluster. 5. Determine the resulting efficiency using several metrics (e.g. throughput, communication latency). 6. Compare the performance penalty of Virtualization versus the hardware cost of the tradition approach. |

|

|

DELIVERABLES: |

Benchmarking implementation structure and code repository. Performance comparison report. |

|

|

SKILLS/REQUIREMENTS: |

Programming / parallel computing |

|

|

EXTRA INFORMATION: |

Reserved for Matthew Cawood |

|

|

AREA: |

HPC |

|

Legacy Topics – l (ask before selecting)

None of these topics, except SW-24, have been done before; but I’m still interesting in supervising one of them if there is sufficient interest in the topic. For SW-24 a start was made, but it can be significantly improved on or re-implemented following a more optimal design.

|

ID: |

SW-20 l |

|

TITLE: |

LURCCI – Level-floor Undercover Robot Crawler Controlled by Internet (phase 1) |

|

DESCRIPTION: |

The plan for the LURCCI project is to develop a robot crawler that is controlled remotely via internet, intended for moving around indoors on even floors. The LURCCI robot can be built from a do-it-yourself robotics kit, which includes the chassis, and drive mechanism for moving and steering the robot – together this provides a platform on which further functionality is built. Other features would be needed to make the robot more useful. This project is design around multiple phases, each phase could be done by a different student working in parallel or in subsequent years.

This is the first time this project is being offered, and consequently, phases 1 and 2 are the requirements for this edition of the project. However, the full set of phases for the robot can be sent to you on request.

Phase 1: Assembling the robot kit, getting the platform together and tested. Control movement of platform via a RS2332 tether. Testing speed, manoeuvrability, battery life. Phase 2: Vision sensor. Adding 1x camera to front of robot which will be used in later projects to enable remote control. A webcam for the first prototype or a small COTS CCD camera kit can be used (ideally this camera should be hooked up to a microcontroller running on the robot, but due to time constrains this may need to be done by a future student working taking the project further). |

|

DELIVERABLES: |

Prototyped LURCII able to move around via manual PC control |

|

SKILLS/REQUIREMENTS: |

Mechatronics, programming |

|

EXTRA INFORMATION: |

|

|

AREA: |

Mechatronics |

|

ID: |

SW-21 l |

|

|

TITLE: |

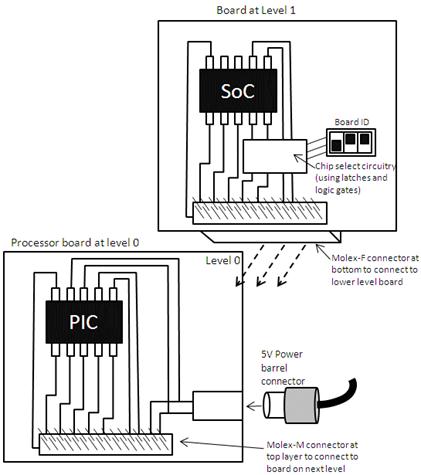

SPI-Ladder: an embedded system rapid prototyping strategy |

|

|

DESCRIPTION: |

The SPI-Ladder project focuses on developing an embedded system

rapid prototyping platform design in order to construct and test products

constructed from a set of SPI system on chip (SoC) components (see

illustration below). Nowadays, SPI components are

widely accessible and low cost. The ease of the SPI protocol, and

the fairly fault-tolerant communications system built into most of these

SoCs, together with the simple hardware wiring, makes SPI an ideal

interfacing system and for a variety of electronic applications.

Figure: Concept sketch for SPI-Ladder prototyping system

Development and testing plans: as the figure above indicates, few electronic parts are expected to be necessary, although there may be a need to convert the 5V input to other levels depending on the PIC processor and SoCs chosen for testing. As illustrated, molex connectors are suggested as a means to both conenect comms and power between board levels as well as a means to hold the boards together. |

|

|

DELIVERABLES: |

PCB / circuit board. Considering the simplicity of the design, it is likely that veriboard can be used to construct the prototyped board levels, although doing so may need a different type of connector (i.e. other than molex) between levels, possibly just simply soldering separate wires. The research-based part of the project can involve analysing speeds and determining to what expect this proposed system is actually usable. This would be written up in your thesis. |

|

|

SKILLS/REQUIREMENTS: |

Embedded systems development, circuit design and prototyping, C programming |

|

|

EXTRA INFO: |

|

|

|

AREA: |

Embedded Systems |

|

|

ID: |

SW-22 l |

|

|

TITLE: |

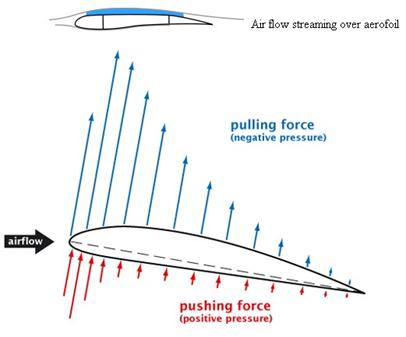

Aerofoil Fluid Flow Simulation (AFFS) |

|

|

DESCRIPTION: |

Development of a scientific modelling application for specifying a variety of parameters such as aerofoil dimensions, wind and movement direction, attitude. The student would need to develop a library of aerofoil structures that users can load, modify and run through the simulator using a variety of conditions. Note that this application is not expected to be highly comprehensive giving very accurate results; there are existing modelling programs to do this (which cost quite a bit) including MatLab’s fluid flow libraries that provide many of the underlying functions. The diagram below illustrates aerofoil cross sections and a selection of relevant parameters.

Figure: Aerofoils and fluid flow of air movement around them

The focus is on approximated results, using mostly static parameters; for example when a helicopter takes off, there are complex ground effect parameters that have very dynamic conditions together with many fine control adjustments taking place – but this sort of comprehensive simulation won’t be done. Rather, two input file formats need to be developed: one to describe the aerofoil, the other to describe the airflow and simulation parameters. The program needs to output simulation results indicating for example pulling, pushing forces vectors, overall lift force, vibration. |

|

|

DELIVERABLES: |

Simulation application, short user manual, description of aerofoil simulation file formats, tutorial giving example for using the system. |

|

|

SKILLS/ REQUIREMENTS: |

Signal processing, MPI, OCTAVE or C/C++ programming |

|

|

EXTRA INFOR: |

|

|

|

AREA: |

Compute Engineering / High performance computing |

|

|

ID: |

SW-23 l |

|

TITLE: |

BEC - Blocks to Embedded C code in a visual way(Alternate title: An experimental in visualizing and generating parallel code) (a community support theme) |

|

DESCRIPTION: |

This project focuses on transforming a block diagram into C code

templates that an embedded software programmer can use to experiment with

communication interfaces and data flows between parts of an embedded

program. This automated C code file generation would saves time for the

programmers and provides a C-code view of communication links modelled. While

this project may seem like a lot of work, much of this effort has

already been provided and is easily accessible in terms of

drawing models and translating them to text. Specifically, the Institute

for Software Integrated Systems (ISIS) has developed a highly customizable

'generic modelling environment' (GME) that can be used to create customised

visual models (e.g., block & line diagrams) that can be automatically

converted into a other forms (e.g. C code or XML). |

|

DELIVERABLES: |

· Specification of the proposed modelling language (include in thesis write-up) · Design of model interpreter (flowcharts, procedure for how the model is converted into C code that can be compiled & executed) · A prototyped model interpreter built using the GME environment (only needs to handle a subset of the language) |

|

SKILLS/REQUIREMENTS: |

Good C++ programming; understanding of parallel programming |

|

EXTRA INFORMATION: |

|

|

AREA: |

Parallel programming |

|

ID: |

SW-24 l |

|

|

TITLE: |

ESPPA - Embedded Systems Past

Projects Archive |

|

|

DESCRIPTION: |

The EEE3074W course, which some of you may have been through and remember, involves an embedded systems prototyping project. From these prototype projects, lots of useful code and information is found related to the platforms used in the course. This project is about developing a web-based archive and search feature that could be used to make better use of these resources. For a sample starting point, which has already been put together, see the EEE3074W Past Projects Archive. |

|

|

DELIVERABLES: |

Online and searchable archive populated with a selection of past projects. |

|

|

SKILLS/REQUIREMENTS: |

Understanding of embedded systems coding (so that you can understand how to organise the data), database design; Data mining; CGI/PHP scripting or web server programming. |

|

|

EXTRA INFORMATION: |

|

|

|

AREA: |

Embedded systems; Data mining |

|

|

ID: |

SW-25 l |

|

|

TITLE: |

NPBBS – Number Plate Based Billing

Parking |

|

|

DESCRIPTION: |

This project focuses on developing an image processing system that can detect car number plates in a photo and output the number as a string of characters. This system needs to have a well-defined interface (e.g. socket-based interface) so that it can be integrated quickly with other processing systems (e.g. for use with a car parking and payment system).

The objective is to prototype a system that could be used for billing people for parking without having to use parking tickets. |

|

|

DELIVERABLES: |

Operational NPBBS prototype |

|

|

SKILLS/REQUIREMENTS: |

Understanding of signal processing techniques. Numerical methods. TCP/IP sockets programming. |

|

|

EXTRA INFORMATION: |

|

|

|

AREA: |

Signal processing, Image processing, network service programming |

|

|

ID: |

SW-26 l |

|

|

TITLE: |

Sound Guard |

|

|

DESCRIPTION: |

This project involves prototyping an embedded system product. The ‘sound guard’ product is intended to be a small, low power device that listens in to an environment. It characterises usual sounds of the environment based on time of day. It continuously maintains a recorded history from a few minutes ago. Unusual sounds, or trigger events (such as an explosion or door opening at an unusual time of night) has its past few minutes of recorded sounds saved and an alarm condition is set. For this prototype, the alarm could just be sending a message over a serial port – a refined version could transmit a wireless alarm or Internet message that includes the device’s location information and the past few minutes of recorded sound. |

|

|

DELIVERABLES: |

Prototype |

|

|

SKILLS/REQUIREMENTS: |

Programming, embedded systems |

|

|

EXTRA INFORMATION: |

|

|

|

AREA: |

Computer Engineering |

|