## A High Speed Data Acquisition System

Andrew Martens

A dissertation submitted to the Department of Electrical Engineering,

University of Cape Town, in fulfilment of the requirements

for the degree of Master of Science in Engineering.

Cape Town, February 2005

## Declaration

I declare that this dissertation is my own, unaided work. It is being submitted for the degree of Master of Science in Engineering in the University of Cape Town. It has not been submitted before for any degree or examination in any other university.

Signature of Author .....

Cape Town 1 February 2005

## Acknowledgements

Thanks go to the University of Cape Town for allowing me the opportunity to further my studies. I am also grateful to Openfuel for giving me time off from real work to finish areas of this dissertation. On a personal note, thanks are given to my family, girlfriend and friends for their support.

# Contents

| $\mathbf{D}$ | eclar             | ation   |                                                   | i  |

|--------------|-------------------|---------|---------------------------------------------------|----|

| A            | ckno <sup>.</sup> | wledge  | ements                                            | ii |

| Ν            | omer              | ıclatur | e.                                                | x  |

| 1            | Intr              | oduct   | ion                                               | 1  |

|              | 1.1               | Overv   | iew                                               | 1  |

|              |                   | 1.1.1   | System Design and Implementation                  | 2  |

|              |                   | 1.1.2   | Testing and Results                               | 2  |

|              |                   | 1.1.3   | Conclusions and Recommendations                   | 3  |

|              |                   | 1.1.4   | High Speed Firmware Design Techniques             | 3  |

|              |                   | 1.1.5   | Analogue to Digital Converter Performance Testing | 5  |

|              |                   | 1.1.6   | Buffer and Data Path Design                       | 5  |

|              | 1.2               | Accon   | npanying CD                                       | 5  |

|              | 1.3               | Concl   | usion                                             | 5  |

| <b>2</b>     | $\mathbf{Sys}$    | tem D   | esign and Implementation                          | 6  |

|              | 2.1               | Syster  | m Requirements                                    | 6  |

|              |                   | 2.1.1   | Functional Requirements                           | 6  |

|              |                   | 2.1.2   | Structural Requirements                           | 7  |

|              | 2.2               | Syster  | m Operation                                       | 7  |

|              |                   | 2.2.1   | Data Capture                                      | 7  |

|   |                   | 2.2.2                                                                                    | Data Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9                                                                                                          |

|---|-------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

|   | 2.3               | Config                                                                                   | guration Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10                                                                                                         |

|   | 2.4               | Hardw                                                                                    | vare                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 10                                                                                                         |

|   |                   | 2.4.1                                                                                    | The ADC Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11                                                                                                         |

|   |                   | 2.4.2                                                                                    | The PMC to PCI Adapter Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 11                                                                                                         |

|   |                   | 2.4.3                                                                                    | The Host Computer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 11                                                                                                         |

|   | 2.5               | Softwa                                                                                   | are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 12                                                                                                         |

|   |                   | 2.5.1                                                                                    | The PCI Device Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12                                                                                                         |

|   |                   | 2.5.2                                                                                    | The Data Capture Suite                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 13                                                                                                         |

|   | 2.6               | Firmw                                                                                    | vare                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 13                                                                                                         |

|   |                   | 2.6.1                                                                                    | Challenges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 14                                                                                                         |

|   |                   | 2.6.2                                                                                    | Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 16                                                                                                         |

|   |                   | 2.6.3                                                                                    | Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 17                                                                                                         |

|   | 2.7               | Conclu                                                                                   | usion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 22                                                                                                         |

|   |                   |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                            |

|   |                   |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                            |

| 3 | Fun               |                                                                                          | lity Tests and Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 23                                                                                                         |

| 3 | <b>Fun</b><br>3.1 |                                                                                          | lity Tests and Results<br>Format Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                            |

| 3 |                   |                                                                                          | v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 23                                                                                                         |

| 3 |                   | Data I                                                                                   | Format Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 23                                                                                                         |

| 3 |                   | Data 1<br>3.1.1<br>3.1.2                                                                 | Format Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 23<br>24                                                                                                   |

| 3 | 3.1               | Data 1<br>3.1.1<br>3.1.2                                                                 | Format Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 23<br>24<br>25                                                                                             |

| 3 | 3.1               | Data 1<br>3.1.1<br>3.1.2<br>Buffer                                                       | Format Tests       Method       Results       Overflow Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <ul><li>23</li><li>24</li><li>25</li><li>25</li></ul>                                                      |

| 3 | 3.1               | Data 1<br>3.1.1<br>3.1.2<br>Buffer<br>3.2.1                                              | Format Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <ol> <li>23</li> <li>24</li> <li>25</li> <li>25</li> <li>25</li> </ol>                                     |

| 3 | 3.1               | Data 1<br>3.1.1<br>3.1.2<br>Buffer<br>3.2.1<br>3.2.2<br>3.2.3                            | Format Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <ol> <li>23</li> <li>24</li> <li>25</li> <li>25</li> <li>25</li> <li>25</li> </ol>                         |

| 3 | 3.1<br>3.2        | Data 1<br>3.1.1<br>3.1.2<br>Buffer<br>3.2.1<br>3.2.2<br>3.2.3                            | Format Tests   Method   Method   Results   Overflow Tests   .   Method   .   .   Method   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   . <td><ol> <li>23</li> <li>24</li> <li>25</li> <li>25</li> <li>25</li> <li>25</li> <li>26</li> </ol></td>                                                                                                                                                                             | <ol> <li>23</li> <li>24</li> <li>25</li> <li>25</li> <li>25</li> <li>25</li> <li>26</li> </ol>             |

| 3 | 3.1<br>3.2        | Data 1<br>3.1.1<br>3.1.2<br>Buffer<br>3.2.1<br>3.2.2<br>3.2.3<br>Unbro                   | Format Tests   Method   Results   Overflow Tests   Method   Method | <ol> <li>23</li> <li>24</li> <li>25</li> <li>25</li> <li>25</li> <li>26</li> <li>26</li> </ol>             |

| 3 | 3.1<br>3.2        | Data 1<br>3.1.1<br>3.1.2<br>Buffer<br>3.2.1<br>3.2.2<br>3.2.3<br>Unbro<br>3.3.1<br>3.3.2 | Format Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <ol> <li>23</li> <li>24</li> <li>25</li> <li>25</li> <li>25</li> <li>26</li> <li>26</li> <li>27</li> </ol> |

|   |                                 | 3.4.2 Level Trigger           | 27                                                        |

|---|---------------------------------|-------------------------------|-----------------------------------------------------------|

|   | 3.5                             | Conclusion                    | 28                                                        |

| 4 | Per                             | formance Tests and Results    | 29                                                        |

|   | 4.1                             | Block Sizes and Data Rates    | 29                                                        |

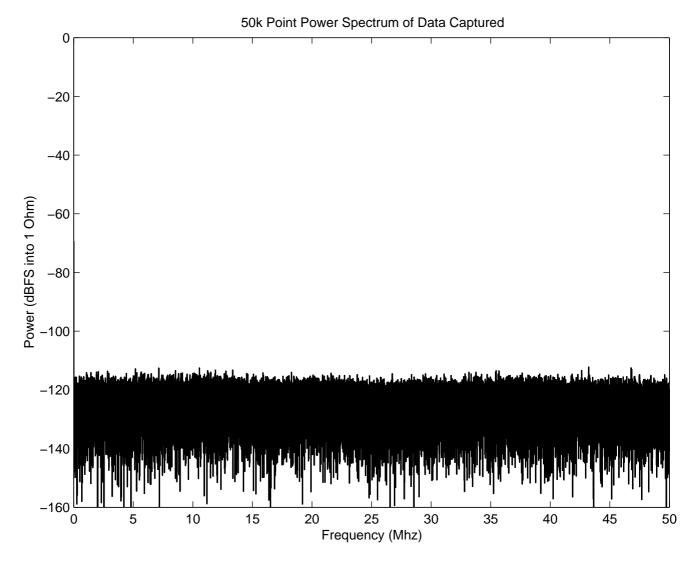

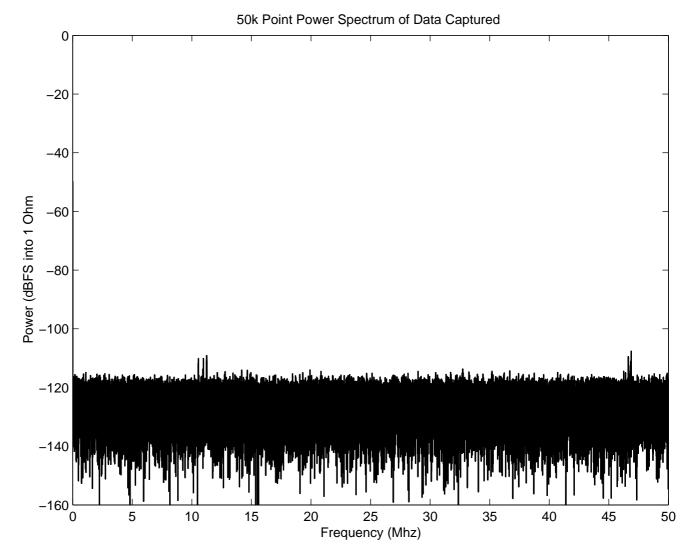

|   | 4.2                             | Grounded Input Test           | 29                                                        |

|   |                                 | 4.2.1 Method                  | 30                                                        |

|   |                                 | 4.2.2 Results                 | 30                                                        |

|   |                                 | 4.2.3 Discussion              | 30                                                        |

|   | 4.3                             | Single Tone Test              | 33                                                        |

|   |                                 | 4.3.1 Method                  | 33                                                        |

|   |                                 | 4.3.2 Results                 | 33                                                        |

|   |                                 | 4.3.3 Discussion              | 39                                                        |

|   | 4.4                             | Conclusion                    | 43                                                        |

|   |                                 |                               |                                                           |

| 5 | Con                             | clusions and Recommendations  | 46                                                        |

| 5 | <b>Con</b><br>5.1               | aclusions and Recommendations |                                                           |

| 5 |                                 |                               | 46                                                        |

|   | 5.1<br>5.2                      | System Performance            | 46                                                        |

|   | 5.1<br>5.2<br><b>Hig</b>        | System Performance            | 46<br>47<br><b>48</b>                                     |

|   | 5.1<br>5.2<br><b>Hig</b>        | System Performance            | 46<br>47<br><b>48</b>                                     |

|   | 5.1<br>5.2<br><b>Hig</b>        | System Performance            | 46<br>47<br><b>48</b><br>48                               |

|   | 5.1<br>5.2<br><b>Hig</b>        | System Performance            | 46<br>47<br><b>48</b><br>48<br>48                         |

|   | 5.1<br>5.2<br><b>Hig</b>        | System Performance            | 46<br>47<br><b>48</b><br>48<br>48<br>48                   |

|   | 5.1<br>5.2<br><b>Hig</b><br>A.1 | System Performance            | 46<br>47<br><b>48</b><br>48<br>48<br>49<br>49             |

|   | 5.1<br>5.2<br><b>Hig</b><br>A.1 | System Performance            | 46<br>47<br><b>48</b><br>48<br>48<br>49<br>49<br>50       |

|   | 5.1<br>5.2<br><b>Hig</b><br>A.1 | System Performance            | 46<br>47<br><b>48</b><br>48<br>48<br>49<br>49<br>50<br>50 |

| В            | Ana   | logue   | to Digital Converter Performance Testing                                                | 53 |

|--------------|-------|---------|-----------------------------------------------------------------------------------------|----|

|              | B.1   | Spectr  | al Analysis                                                                             | 53 |

|              |       | B.1.1   | Time Domain Sampling                                                                    | 53 |

|              |       | B.1.2   | Frequency Domain Sampling                                                               | 54 |

|              |       | B.1.3   | Relationship between the Continuous Fourier Transform and<br>the Fast Fourier Transform | 54 |

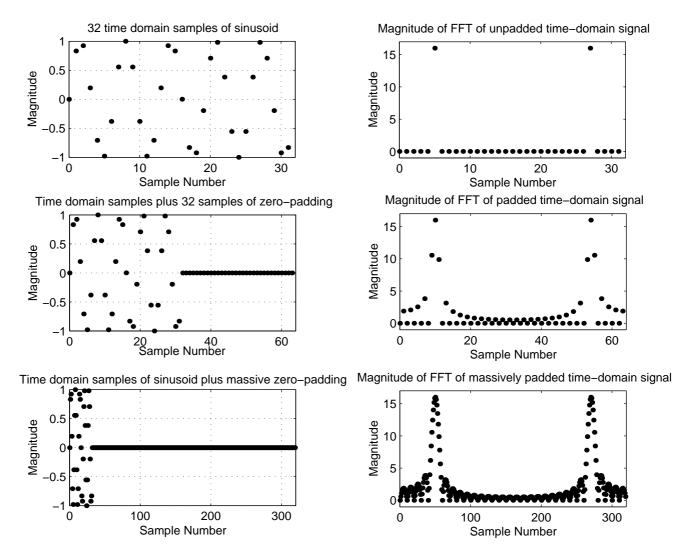

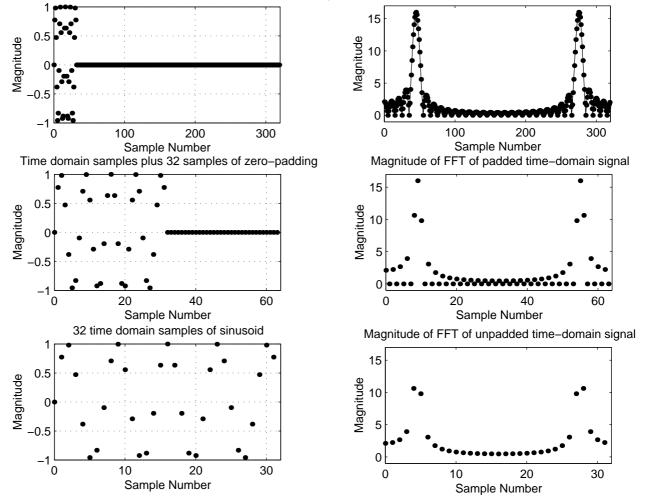

|              |       | B.1.4   | Number of Time Domain Samples                                                           | 56 |

|              |       | B.1.5   | Windowing                                                                               | 57 |

|              | B.2   | Standa  | ard Performance Tests                                                                   | 60 |

|              |       | B.2.1   | Single Tone Test                                                                        | 60 |

|              |       | B.2.2   | Grounded Input Test                                                                     | 65 |

|              |       | B.2.3   | Multi-tone Test                                                                         | 65 |

| $\mathbf{C}$ | Buf   | fer and | l Data Path Design                                                                      | 66 |

|              | C.1   | Task    |                                                                                         | 66 |

|              | C.2   | Resour  | rces                                                                                    | 66 |

|              | C.3   | Desigr  | 1                                                                                       | 67 |

| Bi           | bliog | graphy  |                                                                                         | 72 |

# List of Figures

| 2.1  | Block diagram of system                                               | 8  |

|------|-----------------------------------------------------------------------|----|

| 2.2  | Data format of captured data                                          | 10 |

| 2.3  | Firmware system modules                                               | 18 |

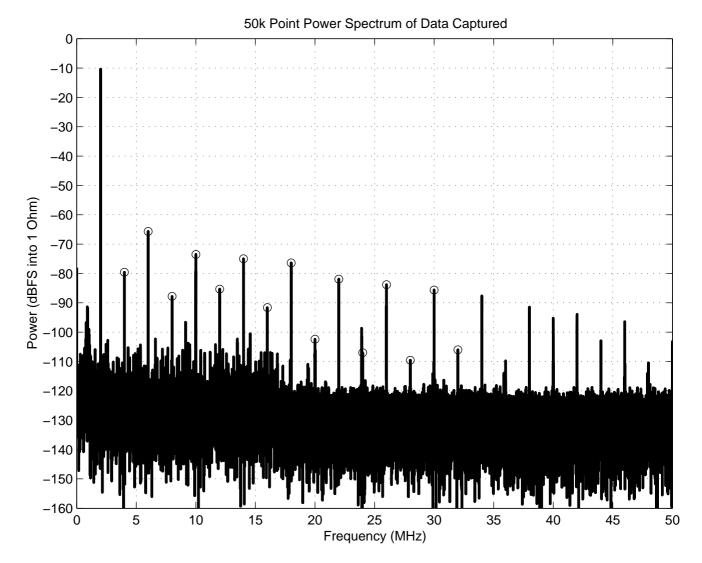

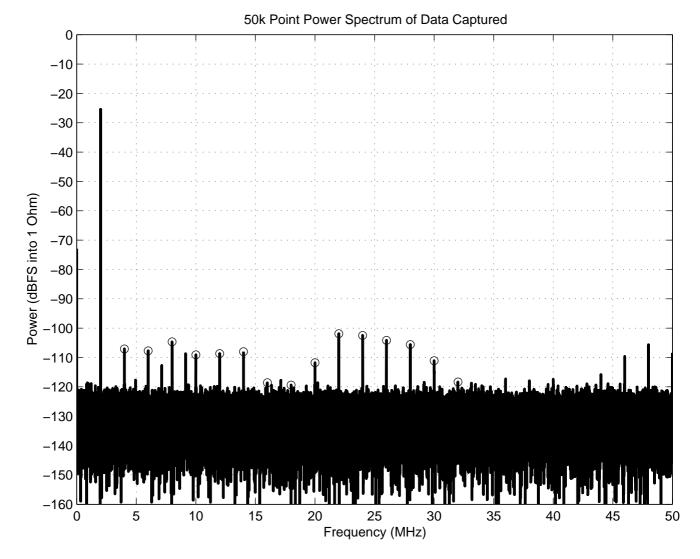

| 4.1  | Grounded input results for channel A                                  | 31 |

| 4.2  | Grounded input results for channel B $\hdots$                         | 32 |

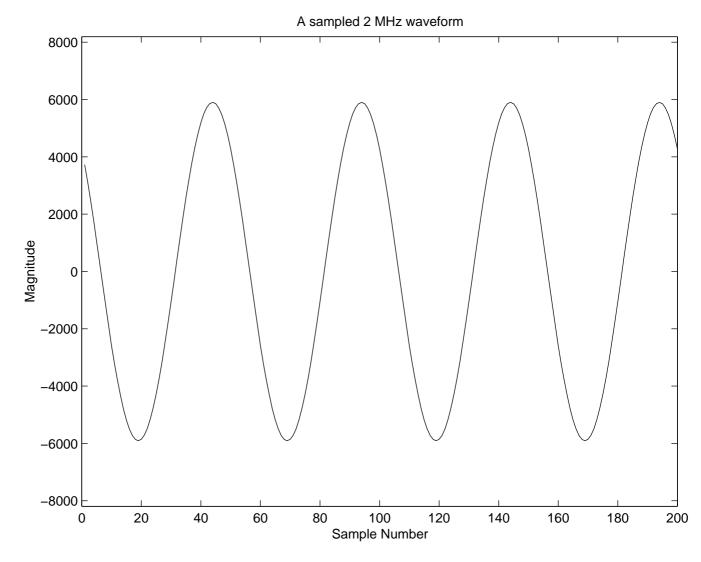

| 4.3  | Captured sine wave in time domain                                     | 34 |

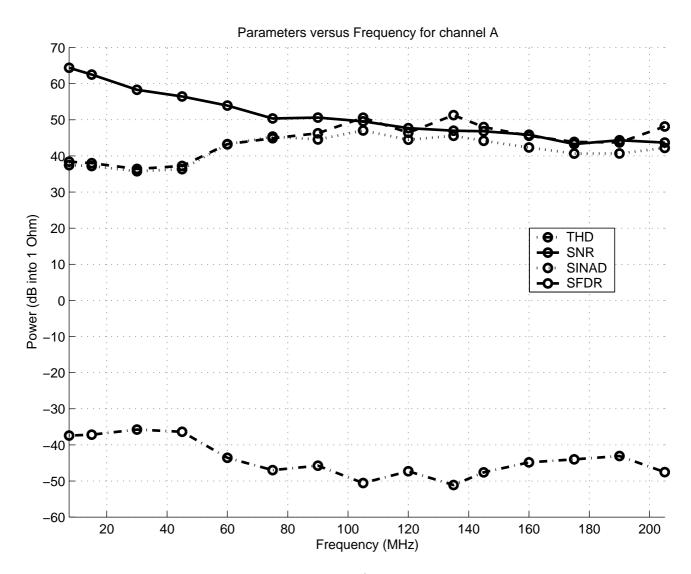

| 4.4  | Channel A performance parameters using HP8656B                        | 35 |

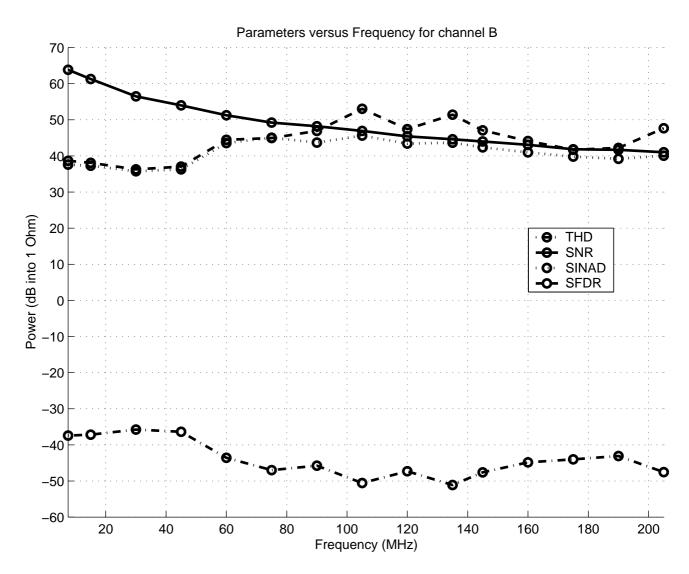

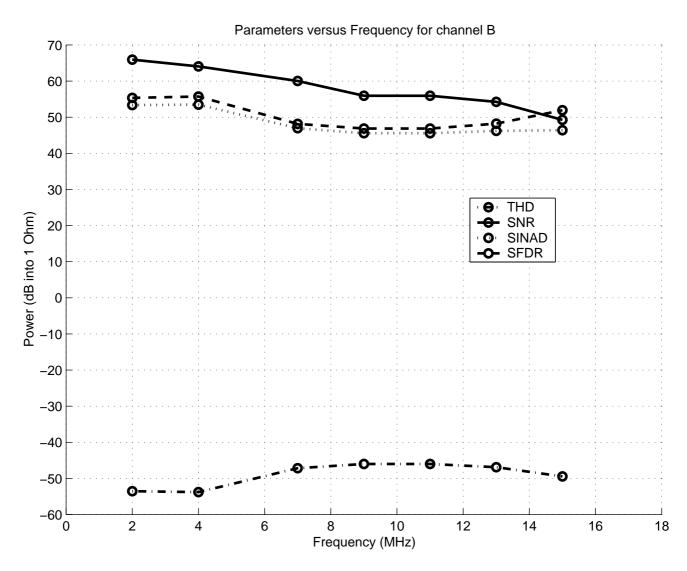

| 4.5  | Channel B performance parameters using HP8656B                        | 36 |

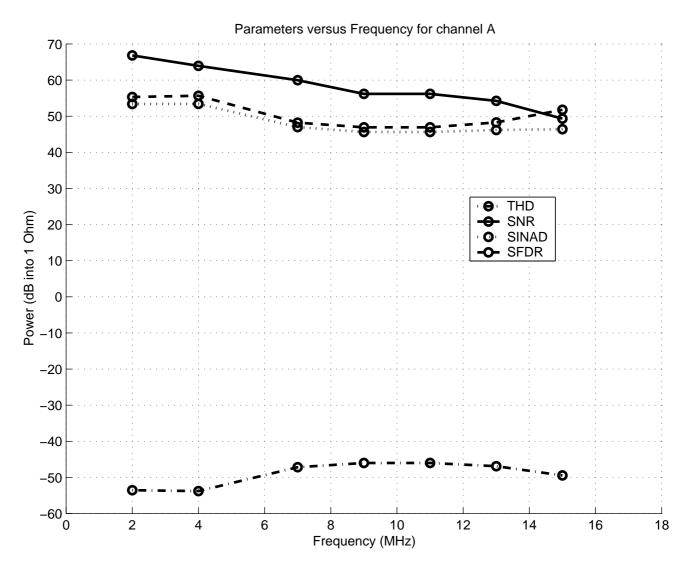

| 4.6  | Channel A performance parameters using HP33120A                       | 37 |

| 4.7  | Channel B performance parameters using HP33120A                       | 38 |

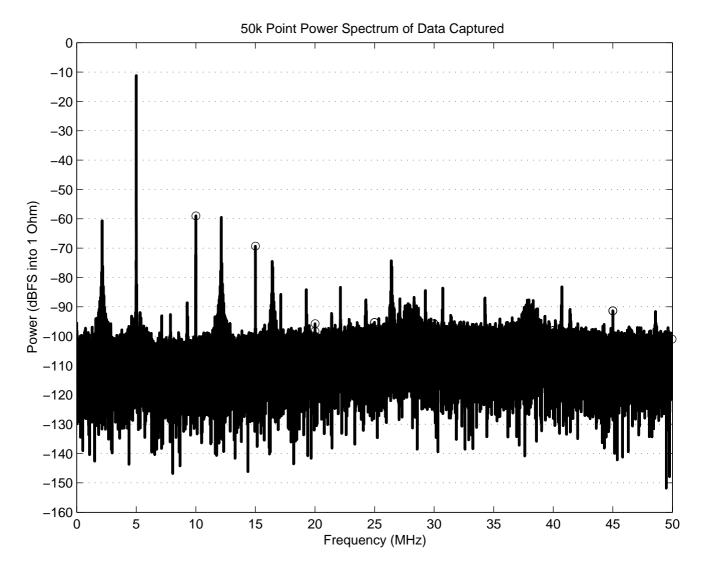

| 4.8  | Captured spectrum from HP8656B                                        | 40 |

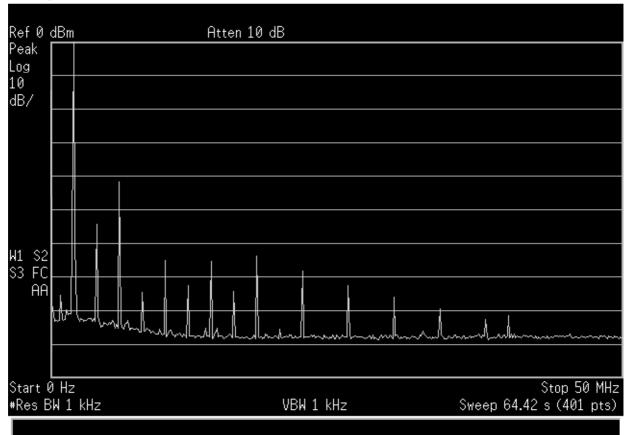

| 4.9  | Spectrum as shown by spectrum analyser                                | 41 |

| 4.10 | Spectrum as shown by system                                           | 42 |

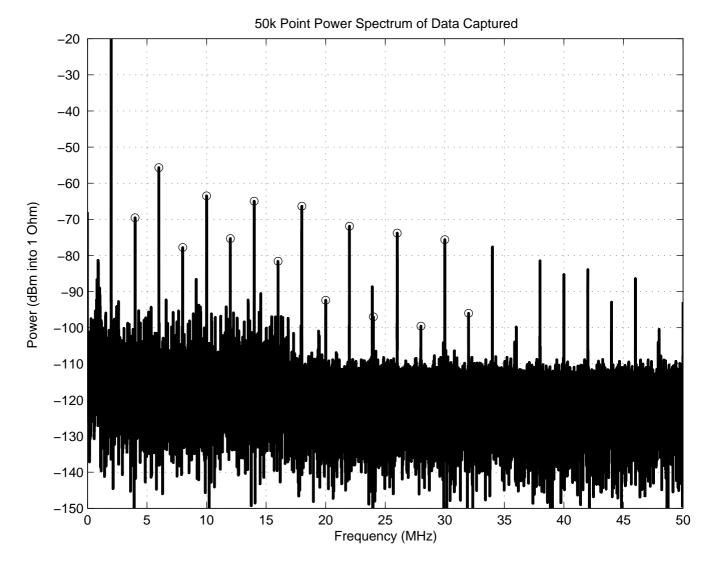

| 4.11 | Spectrum of unfiltered 2 MHz HP33120A signal                          | 44 |

| 4.12 | Spectrum of filtered 2 MHz HP33120A signal                            | 45 |

| B.1  | The effects of zero-padding in FFT results                            | 58 |

| B.2  | The effects of the wrong window function size in FFT results          | 61 |

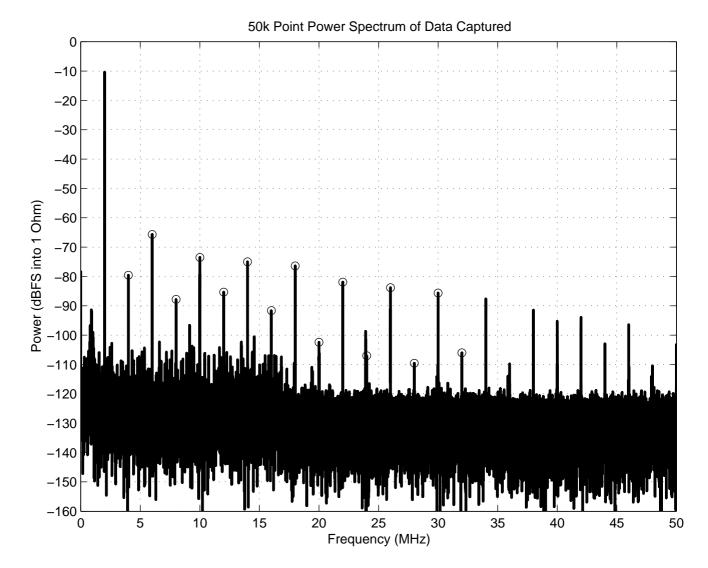

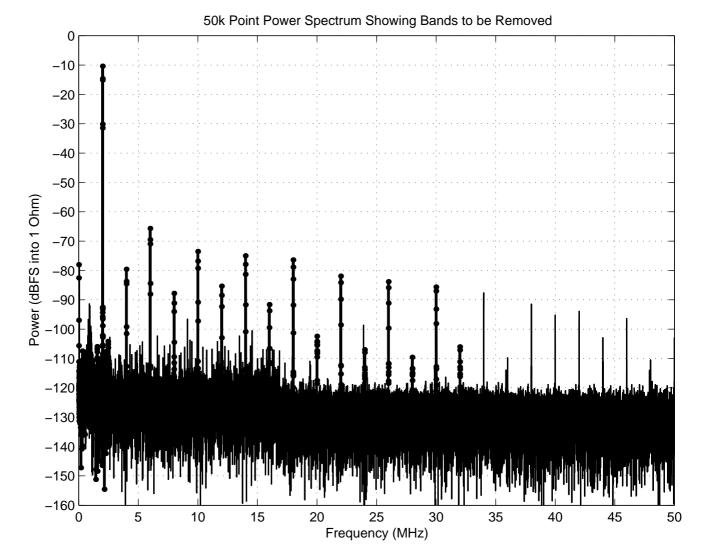

| B.3  | Spectrum of signal showing harmonics                                  | 63 |

| B.4  | Spectrum showing bands to be excluded from noise calculation $\ldots$ | 64 |

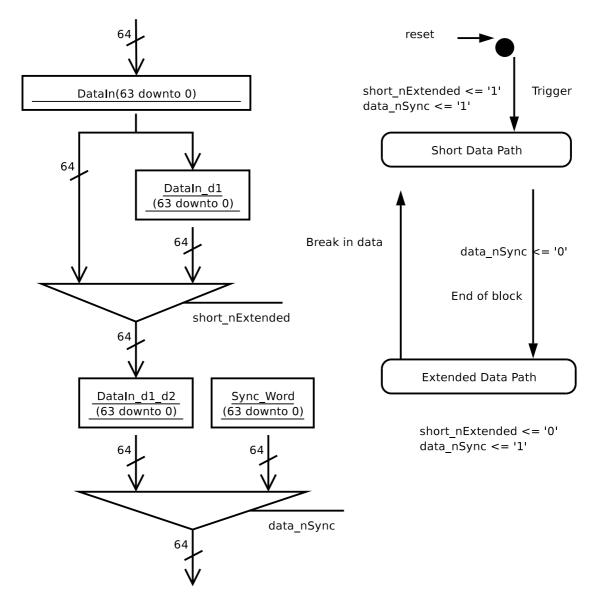

| C.1  | ASMD chart showing synchronisation word logic                         | 68 |

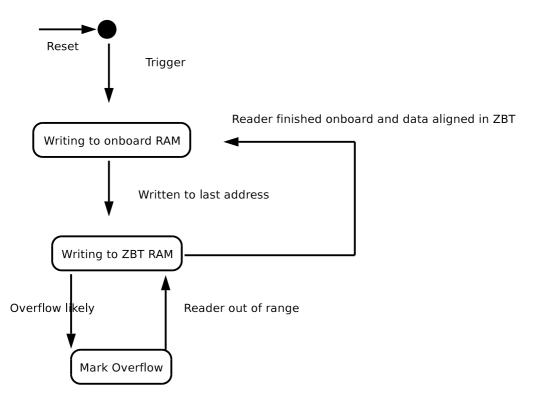

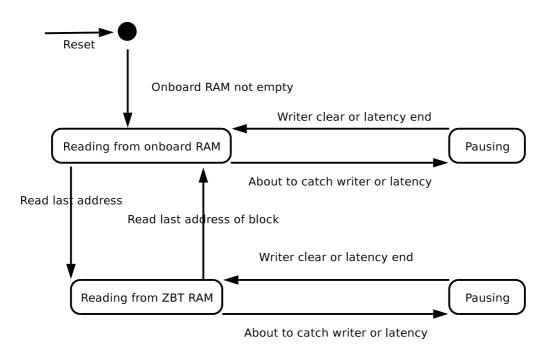

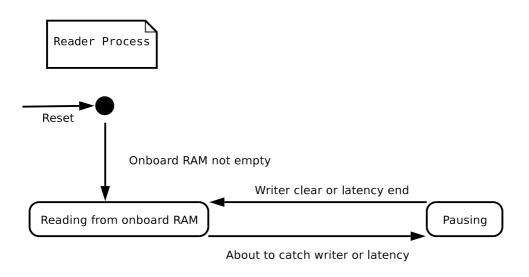

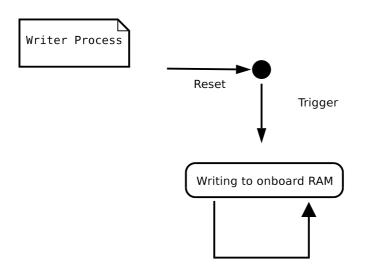

| C.2  | Complex writer process state machine                                  | 69 |

| C.3 | Complex reader process state machine            | 70 |

|-----|-------------------------------------------------|----|

| C.4 | Simple writer and reader process state machines | 71 |

# List of Tables

| 1.1 | Firmware challenges and appropriate design strategies |

|-----|-------------------------------------------------------|

| 1.2 | System functionality test results                     |

| 1.3 | System performance test results                       |

| 2.1 | Firmware module functionality                         |

| 3.1 | Buffer overflow test results                          |

| 5.1 | Summary of system performance                         |

| C.1 | Data path requirements                                |

| C.2 | Storage element resources                             |

## Nomenclature

- **ADC** Analogue to Digital Converter

- ASCII American Standard Code for Information Interchange

- **ASMD charts** Algorithmic State Machine and Data path charts. A means of representing a design that includes a data path and a controller [12]

- $\mathbf{B}$  byte or bytes

- $\mathbf{b}$  bit or bits

- CD Compact Disk

- COTS Commercial-off-the-Shelf

- **DC** Direct Current

- **DMA** Direct Memory Access. A means of transferring data without use of the system's main processor

- dBc Power relative to actual carrier power

- dBFS Power relative to full-scale or the maximum theoretical carrier power

- dBm Power relative to 1 mV

- **ENOB** Effective Number of Bits. See subsection B.2.1

- **FIFO** First-in-First-Out storage structure

- **FPGA** Field Programmable Gate Array

- **G**  $10^9$  (e.g. 1 Gb/s =  $10^9$ bits per second) when referring to data rates.  $2^{30}$  (e.g.  $250 \text{ GB} = 250 \times 2^{30}$ bytes) when referring to data block size

- **GUI** Graphical User Interface

- $k 2^{10}$

- $M 10^6$  (e.g. 100 Mb/s =  $100 \times 10^6$ bits per second) when referring to data rates.  $2^{20}$  (e.g. 10 MB =  $10 \times 2^{20}$  bytes) when referring to data block size

- $\mathbf{PC}$  Personal Computer

- **PCB** Printed Circuit Board

- **PCI** Peripheral Component Interconnect. A standard "that specifies a computer bus for attaching peripheral devices to a computer motherboard" [9].

- PMC PCI Mezzanine Card. "A PCB manufactured to the IEEE P1386.1 standard. This standard combines the electrical characteristics of the PCI bus with mechanical dimensions of the Common Mezzanie Card...format" [8].

- **PMC to PCI adapter card** An adapter card from the PMC form factor to PCI

- **PROM** Programmable Read Only Memory

- **Quadword** 8 bytes

- **RAID** Rendundant Array of Independent Disks

- $\mathbf{RAM}$  Random Access Memory

- SNR Signal to Noise Ratio. See subsection B.2.1

- S Samples or sample

- **SINAD** Signal to Noise and Distortion Ratio. See subsection B.2.1

- **SFDR** Spurious Free Dynamic Range. See subsection B.2.1

- **VHDL** VHSIC Hardware Description Language

- **VHSIC** Very High Speed Integrated Circuit

- Word -2 bytes

- **ZBT RAM** Zeros Bus Turnaround RAM. "Type of SRAM that can read or write every clock cycle to allow 100 percent bus efficiency" [7]

## Chapter 1

## Introduction

Digital systems pervade the world around us. The interface between analogue data sources and these digital systems are the realm of analogue to digital converters (ADCs) that acquire digital snap-shots of data for further processing. Some applications require high sampling rates or high resolution data (or both). In addition to this, certain applications require the capture of large amounts of data.

A good example of an application requiring a high sampling rate and high resolution data, is a digital spectrum analyser used to analyse large bands of a spectrum and offer precise results. Radar systems such as synthetic aperture radars use post-processing techniques on large quantities of data<sup>1</sup>. A developing field requiring versatile data capture systems is that of software defined radio (SDR). It is "a collection of hardware and software technologies that enable reconfigurable system architectures for wireless networks and user terminals" [10]<sup>2</sup>.

This document gives details on a project to build a high speed, high resolution data acquisition system that is capable of performing to some of the most stringent requirements. Specifically, this thesis documents the design, implementation and testing of firmware implemented in an FPGA in a commercial data capture card as part of the system. This firmware would facilitate the real-time transfer of captured data to RAM in a host PC.

## 1.1 Overview

This section gives an overview of the chapters to follow in this document. A brief description along with significant information and findings of each is given in the following subsections.

$<sup>^{1}\</sup>mathrm{See} \ \mathtt{http://rrsg.ee.uct.ac.za/sasar/}$  for an example of such a system

<sup>&</sup>lt;sup>2</sup>An open source Software Defined Radio project is run by the GNU foundation. Details can be found at http://www.gnu.org/software/gnuradio/

### 1.1.1 System Design and Implementation

This chapter is split into various sections detailing the design and implementation of the final system.

The first section of this chapter gives various functional and structural system requirements. These outline a high performance data capture system capable of sampling two channels of data at 100 MHz continuously for up to 5 seconds. The system was to be composed of a commercially available data capture card plugged into a high performance PC. Data would be captured in the data capture card and be passed on via the PC's PCI bus for storage in RAM. Firmware and software would coordinate this transfer.

The following section gives information on system operation during data capture. This process is broken into a number of steps with details on the role different system components play in each step. Details on the format of the resultant data are also given.

Various system configuration options are provided in the following section. These include different data resolutions, trigger sources, clock sources and tag values to be used when marking various events during data capture.

The following section gives detailed information on hardware chosen for the system. Details are provided on the host PC, ADC card and PMC to PCI adapter card used.

Following this is a section giving basic information on the PCI device driver and software application suite implemented to configure the system and coordinate data capture.

The design of the custom firmware necessary to capture, preprocess and forward the data to the rest of the system is then described. Challenges and the design strategies implemented to overcome them are shown in Table 1.1. This section includes details of the various versions of firmware produced in the prototyping design loop used to produce the final version.

## 1.1.2 Testing and Results

The system was tested to check its conformance to requirements and this chapter details the results of these tests. These results are broken into two sections.

The first section details tests to verify the basic functionality of the system. This functionality and the results obtained from the tests are shown in Table 1.2.

The following section relates to the system performance in terms of data rates, captured block sizes and data quality. The results of these tests are summarized in

| Challenge                               | Design strategy employed                     |

|-----------------------------------------|----------------------------------------------|

| Unknown performance of PCI firmware,    | A prototype based system implementa-         |

| PCI bus, operating system and software  | tion strategy was used to design iteratively |

| in terms of sustained data rates.       | higher performance systems.                  |

| Unknown performance of PCI firmware,    | Buffering of data to cater for periodic      |

| PCI bus, operating system and software  | stoppages was implemented. Firmware          |

| in terms of latencies.                  | was designed to cater for and recover from   |

|                                         | occasional data loss. Buffer overflow was    |

|                                         | restricted to occur only in the custom       |

|                                         | firmware module.                             |

| Unknown capability of firmware in FPGA  | Firmware was designed to include heavy       |

| to perform to required clock frequency. | pipelining and reduced fan out from reg-     |

|                                         | isters to increase the possible clock fre-   |

|                                         | quency.                                      |

| Time constraint.                        | A Prototyping strategy was used to en-       |

|                                         | sure a working system, even if not at the    |

|                                         | required performance level.                  |

Table 1.1: Firmware challenges and appropriate design strategies

Table 1.3.

## 1.1.3 Conclusions and Recommendations

This final chapter gives conclusions reached about the project. The system is found to conform to specifications with scope for improvement in terms of functionality and performance.

Improvements envisioned for future systems are as follows;

- The use of FPGAs containing a larger amount of RAM or a more appropriate ZBT RAM module to reduce the likelihood of data overflows in the custom firmware module.

- The system should be tested with better quality signal generators and Nyquist filters.

## 1.1.4 High Speed Firmware Design Techniques

During design and implementation, various techniques had to be employed to enable the firmware to perform to the clock frequency required. Factors affecting the speed at which firmware can operate are discussed. This appendix provides information on methods to combat these sources of delay.

| Functionality                                    | Test Results                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data format.                                     | <ul> <li>Data format was found to be predictable. This included format in respect of the following;</li> <li>The position and behaviour of synchronisation flags and the way in which data behaved in their presence.</li> <li>The structure of data with the system operating in different data resolution configurations</li> <li>The placement and structure of overflow markers and the way in which data behaved in their presence.</li> </ul> |

| Transfer start and end.                          | Very large transfers (250 GB) of data were captured without disruption.<br>Multiple (800) transfers were performed successfully with a software<br>generated trigger.                                                                                                                                                                                                                                                                               |

| Trigger sources.                                 | Transfers using the various trigger sources were initiated successfully.                                                                                                                                                                                                                                                                                                                                                                            |

| Overflow detec-<br>tion.                         | Overflows were forced and the system reported them predictably.                                                                                                                                                                                                                                                                                                                                                                                     |

| Successful cap-<br>ture of large data<br>blocks. | Large blocks (2.5 GB) of test data were captured and tested for over-<br>flows in the custom firmware module. The results of the capture of 200<br>blocks at different data resolutions were as follows:                                                                                                                                                                                                                                            |

|                                                  | • At $400 \times 10^6 B/s$ (14 bits per sample plus two padding bits) 8 overflows occurred. The system lost a maximum of 2072 bytes in an overflow.                                                                                                                                                                                                                                                                                                 |

|                                                  | • At $350 \times 10^6 B/s$ (14 bits per sample) 3 overflows occurred. The system lost a maximum of 280 bytes in an overflow.                                                                                                                                                                                                                                                                                                                        |

|                                                  | • At $300 \times 10^6 B/s$ (12 bits per sample) 1 overflow occurred and the system lost 56 bytes.                                                                                                                                                                                                                                                                                                                                                   |

|                                                  | • At $200 \times 10^6 B/s$ (8 bits per sample) no overflows occurred.                                                                                                                                                                                                                                                                                                                                                                               |

| Table 1.9.    | Cristana | functionality | toat | magnita |

|---------------|----------|---------------|------|---------|

| Table $1.2$ : | System   | functionality | test | results |

| Performance Parame- | Test Results                                                             |

|---------------------|--------------------------------------------------------------------------|

| ter                 |                                                                          |

| Data rates.         | The system was tested at data rates up to $400 \times 10^6 B/s$ . The    |

|                     | probability of data loss decreased significantly with reduced data       |

|                     | rates and, at $200 \times 10^6 B/s$ , was almost zero. In all cases data |

|                     | capture was to RAM on the host computer and under as close to            |

|                     | ideal conditions as could be found.                                      |

| Data block sizes.   | 2.5 GB data blocks were captured to the host computer's RAM,             |

|                     | the maximum data block size possible with the RAM available.             |

| ADC performance     | Signal generators were used to generate data that was captured           |

|                     | by the system. Due to the poor quality of this data and lack of          |

|                     | necessary filters, these tests were not conclusive by themselves.        |

Table 1.3: System performance test results

### 1.1.5 Analogue to Digital Converter Performance Testing

An important characteristic of an ADC is the quality of data captured. This involves using standard tests to quantify the quality of the data captured. Spectral analysis and related topics are explored in this appendix as these are crucial to how the tests are performed and how results are interpreted. The tests themselves are then described which include the single, multi-tone and grounded-input tests.

### 1.1.6 Buffer and Data Path Design

This appendix gives detailed information on the data path designed in the custom firmware. It firstly gives the functionality the data path had to implement. The various resources available to accomplish these requirements are then provided. A final design is then described that attempts to cater for all requirements with the resources supplied.

## 1.2 Accompanying CD

A CD is provided with this thesis. It contains the following directories as well as a version of this thesis in electronic format.

- 'firmware' Files containing all modules implemented in the final system are present in this directory. Modules related to the ZBT RAM, although not used in the final system, are included for reference. These modules are implemented in VHDL and the final system synthesized and routed using Quartus II version 3.0 with service pack 1 installed from Altera.

- 'software' This directory contains the source for small C programs used in debugging and testing the system. A program to convert binary data in 14 bit (with padding bits) data resolution to ASCII data usable by Matlab is also included.

- **'Matlab scripts'** Matlab was used in testing the data quality capabilities of the system. This directory contains the scripts used.

## 1.3 Conclusion

This chapter has briefly introduced the system under design and given an overview of the chapters to follow. The next chapter starts with detailed system requirements and then details the design and implementation of the system.

## Chapter 2

## System Design and Implementation

This chapter begins with a set of requirements the final system was to adhere to including a high level description of the required system structure. This is followed by a description of system operation during data capture for the system implemented. Included in this discussion is a description of the format of resultant data. Following are sections giving details on hardware, software and firmware system components. Various possible system configuration options are given in the final section.

## 2.1 System Requirements

This section gives the set of requirements for the system. These are taken from [14]. It also gives a description of the hardware to be used and the basic system structure.

### 2.1.1 Functional Requirements

Time to completion The system was to be finished as soon as possible

- **Data resolution** The data resolution did not need to be very high for the target application. Better resolution data would produce better results however.

- **Sample rate** The minimum sampling rate would be  $100 \times 10^6$  samples per second per channel for two channels of data.

- **Time stamping** Time stamping would be required to check for lost data. Data would be produced in blocks with each block having a unique identifier. A 16 bit counter placed approximately every 1000 samples would be sufficient.

- **Triggering** The triggering instant did not have to be exact. Data would be captured and post-processing used for synchronisation. A trigger generated by

software would be sufficient. A trigger relying on the voltage level read by the ADCs could also be useful.

- Length of capture This should be programmable. In this application, a block representing about five seconds of continual capture was required.

- Host computer This would be determined by data capture and storage requirements.

- **Software compatibility** The main software requirement was that resultant data should be available in a format for processing in a C program or Matlab. A means of configuring the system via software would be necessary.

Mechanical The required system did not have any mechanical constraints.

#### 2.1.2 Structural Requirements

The system was to be designed using an ADC card that had been used in a previous project. This was the PM480 produced by Parsec (see http://www.parsec.co.za for the latest information on this card). Figure 2.1 shows a block diagram of the required system. The PM480 would plug into a PMC to PCI adapter card and this would plug into a PCI slot in a host computer running Linux. The PM480 contained firmware supplied by the manufacturer to perform PCI transactions. This firmware allowed data to be transferred between a PCI driver on the host computer, and custom firmware on the PM480. This custom firmware would be implemented to capture data and send it on for transfer to RAM of the host computer. The custom firmware was the responsibility of the author and is the main focus of this document although many aspects of the whole system are discussed. A colleague was to implement the PCI driver as well as other software to ease the task of system configuration and data capture.

## 2.2 System Operation

This section gives details on system operation. Steps taken during data capture as well as the roles played by various system components are provided in the first subsection. The second subsection provides information on the format of the resultant data.

#### 2.2.1 Data Capture

The sequence of operations taken during the capture of data would be as follows:

Figure 2.1: Block diagram of system

- 1. A user space application would be started that would prompt the user for various configuration options. This application would then configure the system for optimal performance and load the PCI device driver using appropriate arguments. The driver would use the configuration settings passed to it to configure parts of the system under its control.

- 2. The user space application would then wait for data transfer to complete via the device driver. Data transfer would start when the custom firmware received a trigger to start capture. The trigger source would be configurable. (See section 2.3 for information on these options). If a time to start capture was provided, the trigger would be generated by the application software at the correct time.

- 3. When data transfer begins, the custom firmware would take a reading from each data source every clock cycle and pass these samples on for buffering. The data would then be read out of the buffer and passed on to a buffer in the PCI firmware module for transfer on via the PCI subsystem.

- 4. The control unit controlling reads and writes to the custom firmware's buffer would monitor the level of this buffer and control reading from the custom firmware's buffer to prevent overflows. If the custom firmware's buffer was about to overflow, further writes would be prevented and a marker inserted into the data to indicate the location and size of the overflow.

- 5. The amount of data being transferred would be monitored and a marker

inserted into the data at regular intervals before passing it on to the PCI firmware.

- 6. The firmware transferring data to the host computer via the PCI subsystem would transfer data directly into RAM.

- 7. Once the required amount of data had been captured, the PCI device driver would oversee the suspension of data capture. The user space application would then transfer the data from RAM to a file on hard disk, unload the device driver, and return the system to its normal configuration.

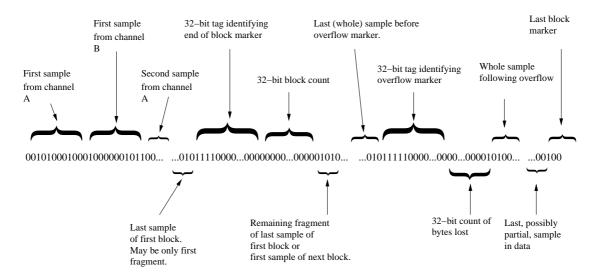

### 2.2.2 Data Format

Data would be broken into 'blocks' of uniform size containing a specified number of 64 bit quadwords. A marker would be placed at the end of the specified number of quadwords. This marker would be a quadword itself and contained a 32 bit tag, that would help to identify the quadword as a marker, and a 32 bit counter identifying the block's position in the data stream. This marker is referred to as a 'block marker', 'end of block marker' or 'synchronisation word' in the text that follows.

Data from each channel would be interleaved so that the first sample from channel 'A' would be followed by the first sample from channel 'B' which would then, in turn, be followed by the second sample from channel 'A' and so on. Data would not be byte-aligned (except where this would be implicit i.e. in the 8 and 14 bit (with two bits of padding) data resolution configurations). Each sample would follow directly after the previous sample. In 14 bit (with padding) data resolution mode, two extra '0' bits would be added 'above' the most significant bit giving 16 bits per data sample. This would help to distinguish data from markers (if the appropriate bits were '1' in the marker). This would also make data extraction easier by forcing data to align to word boundaries .

In the event of an imminent overflow in the buffer in the custom firmware module, data would be discarded and a marker placed in the data stream to mark the place and extent of data loss. This marker would be placed so that there would be no partial sample before or after it (i.e. it would separate complete data samples). It would consist of the same 32 bit tag used to mark the end of a block of data, followed by a 32 bit counter indicating how many bytes had been lost. The data block containing the marker would not be truncated but still contained the correct number of quadwords (one of which would be the overflow marker).

Figure 2.2 shows a data stream of example 12 bit resolution data. The first data sample in the stream is on the left. Details of the first end of block marker and one overflow marker are shown. The beginning and end of the data are also shown.

Figure 2.2: Data format of captured data

## 2.3 Configuration Options

Configuration options for the system were to be as follows:

- The number of quadwords in a data block could be specified.

- The insertion of a tag at the end of every data block could be suppressed.

- The unique 32 bit tag that would be used to mark the end of data blocks and data loss could be set to any value.

- The trigger source could be configured to be from software, an external source or when the data reached a specific level on a data channel.

- The data source could be the ADCs or a firmware module generating test 'ramp' data for debugging.

- The clock source for the ADCs and custom firmware could be an on-board oscillator or an external input.

- The data resolution was to be configurable as 8, 12, 14 bits or 14 bits plus two padding bits.

## 2.4 Hardware

The hardware used in the final system can be divided into three main parts:

• A high speed sampling card containing ADCs to sample the data stream and FPGAs to contain the custom and PCI firmware.

- A PMC to PCI adapter card.

- A computer with a large quantity of RAM, hard drive, processor and good quality motherboard supporting high data rate PCI busses.

### 2.4.1 The ADC Card

The PM480 wdata acquisition card from Parsec was chosen (see http://www.parsec.co.za for more information on the PM480). This included a PCI firmware subsystem that would allow configuration and data transfer. The version of the PM480 usfsed for this project also contained:

- Two ACEX FPGAs

- Two Analog Devices AD6645 ADCs

- A 4 MB ZBT RAM module

- A 100 MHz oscillator and a clock multiplexer allowing the choice between the onboard oscillator and an external input as the clock source

- An external input for supplying a trigger to the custom firmware

#### 2.4.2 The PMC to PCI Adapter Card

An adapter card was needed as the ADC card we were using could not plug directly into a PCI slot as it was in the PMC form-factor. A passive adapter card (the PCI bus lines are merely extended) from another project was used in the first part of development but this proved not up to the task. The system would work only on certain PCs. In others, the entire operating system would lock up during transfer forcing a hard reboot. Certain data blocks would also be 'lost'. Many days were spent debugging and checking firmware and software. The replacement of the passive adapter card with an active one (which implements a PCI bridge on the card) solved all of these problems. The final system used a PMB-P Peritek active PMC to PCI adapter card. See http://www.peritek.com/pmb\_p\_main.htm for more information on this card.

### 2.4.3 The Host Computer

The host computer was chosen for its ability to handle the data rates to be generated. Hard drives did not support the data rates required (performance testing on a highend IBM system using a RAID system yielded a sustained data rate of just over  $170 \times 2^{20}$  B/s when writing a large file) so capture would be to RAM. A good quality PCI chip set and the ability to support a large amount (at least 3 GB) of system RAM was required. An above-average processor was thought to be sufficient. The RAM had to be fast enough to support the data rate and the error-correcting capabilities of the modules chosen was a bonus. The final system consisted of the following:

- An Intel SE7505VB2 (Vero Beach) motherboard supporting one 64-bit, 66 MHz PCI bus.

- A single Xeon 2.4 GHz processor (512 kB cache).

- 3 GB of Transcend ECC266 DDR RAM. 500 MB of this would be allocated for use by software and 2.5 GB made into a RAM disk for data capture.

- A 120 GB 7200 rpm Seagate Barracuda hard drive.

## 2.5 Software

The custom built software was developed in Linux by a colleague and consisted of two main modules:

- A device driver to coordinate the capture of data and configure the system.

- A software suite to get configuration information from the user, load the driver, configure the operating system, unload the driver after capture, and copy data to a file on the hard drive after capture.

## 2.5.1 The PCI Device Driver

The PCI device driver was developed in parallel with the custom firmware. It was designed to be highly configurable so that various settings could be tweaked to improve performance. Two versions were developed starting with a basic, low performance version and moving to a high performance version. This software was extremely useful for testing and debugging. The final version supported the following functions:

• Configuration of the firmware and hardware on loading the module. This allowed the user to specify options like clock source, data resolution, trigger source and data block size.

- Configuration of software resources such as the size and number of internal buffers to allow tweaking.

- Access to status information obtained from various parts of the system at various stages of data capture. This data was used during debugging and tweaking.

### 2.5.2 The Data Capture Suite

The utility developed to aid a user during data capture served various functions:

- It allowed the user to specify a time at which capture should start if it was not to start immediately

- It allowed the user to choose from various system configuration options in a simple manner

- It automatically configured the system for optimum performance

- It loaded the device driver with appropriate configuration options removing the task of learning the various options from the user

It was implemented in two parts:

- 1. An executable that interfaced with the device driver to start and end capture. This executable could take arguments such as what size data block to capture and at what time to start data capture.

- 2. A set of scripts that helped automate the process of configuration and data capture. The set of scripts provided a GUI to obtain the settings from the user. This set of scripts then loaded and configured the device driver for optimum operating conditions. It also configured the other parts of the system for ideal system conditions during capture by performing tasks such as shutting down unneeded processes. It then called the executable with appropriate options for data capture. After capture, it copied the data block to the hard drive for further processing and returned the system to a normal configuration.

## 2.6 Firmware

This section details the design and implementation of the custom firmware responsible for capturing data from the ADCs and sending it on to the PCI firmware. The various challenges associated with this firmware are introduced first along with the design strategy that would attempt to overcome each of these challenges. The actual design on the various firmware modules is then described. The prototyping process used to develop the process is described, with the various prototypes and information used in their design being described.

#### 2.6.1 Challenges

This section gives the various challenges to be overcome when designing the custom firmware as well as the design strategies implemented in an attempt to overcome them. Various smaller challenges were encountered such as designing for metastability, debugging various error conditions, interaction between multiple state machines and others but these are not project specific and are well discussed in other sources.

#### Average data rates

The system to be constructed was reasonably large consisting of many components that were untested at the data rates concerned and whose operation was not under the designer's control. In addition, the entire system was not available at the time of design for testing, portions of it arriving during implementation with low performance substitutes being used in the interim as implementation could not be delayed due to time constraints. This unknown average data was the largest potential challenge. Literature could not be found on reliable transmission of large blocks of data via PCI at  $400 \times 10^6$  B/s (which would be the approximate data rate required) under any conditions. A non-trivial bottleneck at any point would be difficult to cater for, except to attempt replacement with a new system component which would add time and cost to the project. System components that might not perform as needed in this regard were the following:

- The PCI system might not perform to the maximum theoretical data rate due to non-performance of any of the components in the data path. This could be a function of the PCI controllers concerned (it was found through testing that some older PC's supported a lower than theoretical maximum data rate) and the PCI subsystem provided with the ADC card.

- The operating system and application software might not be efficient enough to process the data at the required rate. The main contributor to this would be the performance of the system these would run on. This would be determined by the performance of the processor, cache, RAM and the busses interlinking these components. Another contributor would be the efficiency of software routines including interrupt service and PCI transaction routines. Combined

with these would be competition for resources from devices and processes that would be part of the system. This competition could be reduced but not totally controlled due to the necessary overhead of the operating system.

The design strategy employed to overcome this potential challenge was to develop initial low performance firmware that would not require high performance from the rest of the system. Later prototypes could add to the load placed on the rest of the system as components of the final system became available and previous versions where found to perform adequately.

#### Latencies

If the average data rate was sufficient, the next possible challenge would be if components in the data transfer chain added large latencies during transfer. This would cause the potential loss of data if buffers in the chain overflowed. The components whose operation was unknown could again prove to be the undoing of the system:

- The operating system and application software could have slow turn-around times between processing blocks of data. The non real time performance of the Linux kernel would mean unknown delays in servicing interrupts and time spent running application processes.

- PCI communication is non real time. A PCI controller may grant the bus to a requesting device after an unspecified amount of time [17, page 15] and may force the current bus master to release the bus if it is needed by another device even if in burst mode if the bus master conforms to the recommended PCI specification [17, page 376]. These factors could combine to introduce latencies of an unknown size during transfer.

- The performance of the PCI firmware engine supplied with the ADC card was unknown in terms of time taken to initiate and end transfers.

The strategy used to reduce the probability of buffer overflows was to use as large buffers as possible to absorb occasional disruptions in data flow. The ADC card supplied was not explicitly designed to transfer large blocks of data in real time however, and support for the buffering required was implicit. Another strategy was to design the system to ensure that the system could recover from buffer overflows and continue capturing data. The system was designed so that any overflows would occur in buffers in the custom firmware module exclusively. The custom firmware would ensure that an overflow was marked and that data capture could continue. Software processing the resultant data could check for overflows and act appropriately where they were found to occur.

#### FPGA performance

To capture the data being produced by the ADCs, the custom firmware had to perform at 100 MHz. Parts of the system interacting with the PCI firmware had to perform at 66 MHz. In a previous project using this ADC card, getting the firmware to run at similar clock rates had been found to be a large source of frustration if not planned for. Attempting to speed up a firmware design after implementation was found to be expensive in terms of time and effort. A change in one part of the system often caused a ripple effect of necessary changes in other logic. Each change exposed the firmware to possible bugs and the testing process to fix these wasted a lot of time.

The strategy used to combat this was to design the firmware with high speed in mind. Pipelining was heavily employed and fanout from registers was reduced by forcing redundant logic and registers. See appendix A for information on techniques to increase the possible clock rate in firmware.

#### Time

The customer needed the system as soon as possible. This meant that design, implementation and testing had to proceed as fast as possible. There would not be very much time for redesign in case of system non-performance. Design could also not be put off until all of the necessary components were available and fully tested.

This challenge was overcome by generating an initial low performance prototype and increasing the performance of new prototypes based on test results from previous prototypes and as system components became available. This would ensure that a system would be ready for the customer, even if it performed at a standard that was lower than optimal. This strategy also allowed core functionality to be implemented initially and features added later when basic requirements were met in previous prototypes.

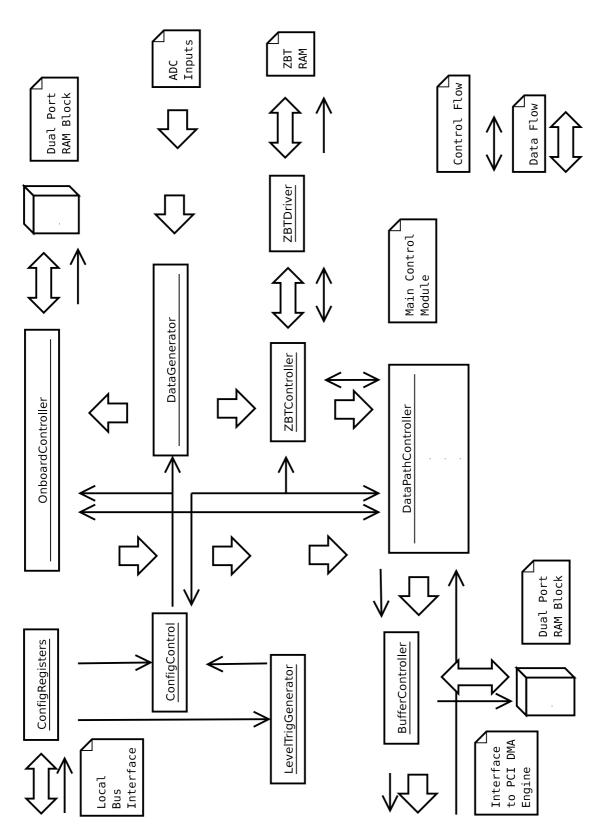

### 2.6.2 Design

The custom firmware was firstly divided into various modules responsible for different actions. In later prototypes, modules would be reused with necessary modifications restricted to modules requiring upgrading. Consistent module interfaces would help in simulation as the same testbenches could be used to test modules from different prototypes. These modules are shown in Figure 2.3. This shows all modules from all prototype systems. Some prototypes did not include all modules. Details on the functionality provided by each module is given in Table 2.1. These modules can be found on the attached CD in the 'firmware' directory in the file with the name given in Table 2.1 (testbenches for each module are found in '<file name>\_tb.vhd' on the CD where '<file name>.vhd' is the name of the file containing the module in the table).

### 2.6.3 Implementation