# Design, Simulation, and Implementation of a Digital Quadrature Demodulator for a Stepped Frequency Radar

by

#### Michael K. Cope

A dissertation submitted to the Department of Electrical Engineering, University of Cape Town, in partial fulfillment of the requirements for the Degree

**Master of Science in Engineering**

**University of Cape Town**

January 2003

Copyright 2003, University of Cape Town

## **Declaration**

I declare that this dissertation is my own, unaided work. It is being submitted for the degree of Master of Science in Engineering at the University of Cape Town. It has not been submitted before for any degree or examination at any other university.

Cape Town, 3 June 2003

### **Abstract**

The scope of this thesis project is the design and implementation of a digital quadrature demodulator for a stepped frequency ground penetrating radar. This dissertation presents a theoretical model of the demodulator, simulations characterising the demodulator performance, as well as the design, construction, and measurement of the prototype demodulator.

The demodulator estimates the amplitude and phase of the intermediate frequency signal of a time-interleaved dual-channel heterodyne radar receiver. A demodulator model is developed from a survey of the relevant literature, paying particular attention to errors introduced in sampling. Simulations predict the demodulator performance in the radar system, suggesting coherent integration improves accuracy by reducing the effect of random sampling errors. The design of the prototype and characterisation of its performance are briefly reported.

Measurements confirmed that coherent integration increased the demodulator accuracy. Timing jitter was found to be the most significant cause of error, due to phase noise in the IF signal. The simulations predicted that the demodulator would not meet the specified performance; measurement determined the prototype's accuracy to be within specification, although the test signals were of higher quality than the expected radar IF signal.

# Acknowledgements

I would like to thank my supervisor, Professor Michael Inggs, for his advice. I also wish to thank Dr Alan Langman for his guidance on technical matters. Thanks also to OpenFuel (Pty) Ltd and the SA National Defence Force for their financial support. I wish to thank my fellow-members of the Radar Remote Sensing Group for their friendship and assistance, in particular Thomas Bennett, Grant Carter, and Leon Alexander. Finally, I am grateful to my family for the love and support extended to me over the last 25 years, which made it all worthwhile.

### **Nomenclature**

ADC - Analogue-to-digital converter

AHDL - Analogue hardware design language

CPLD - Complex programmable logic device

Dacs - Data capture system

dc - direct current

DNL - differential nonlinearity

FPGA - field programmable gate array

GPR - ground penetrating radar

I - in-phase

IC - integrated circuit

IF - intermediate frequency

JTAG - Joint Test Access Group

Q - quadrature

LO - local oscillator

LOS - local oscillator synthesizer

Opamp - operational amplifier

PC - personal computer

RF - radio frequency

rms - root mean square

RRI - ramp repetition interval

SFCW - stepped frequency continuous wave

SNR - signal-to-noise ratio

SRAM - static random access memory

TXS - transmit synthesizer

VHDL - Very High Speed Integrated Circuit Design Language

# **Table of Contents**

| List ( | vii<br>viii                                              |    |

|--------|----------------------------------------------------------|----|

| 1 In   | troduction                                               | 1  |

| 1.1    | Summary                                                  | 1  |

| 1.2    | Ground penetrating radar research at UCT                 | 1  |

| 1.3    | Dissertation outline                                     | 2  |

| 2 Li   | iterature review: digital quadrature demodulation        | 4  |

| 2.1    | Architecture and operation of SFCW radar systems         | 4  |

| 2.2    | Digital quadrature demodulation                          | 5  |

| 2.3    | Modelling the digital quadrature demodulator             | 10 |

| 2.4    | Summary                                                  | 17 |

| 3 Si   | mulating the digital quadrature demodulator              | 18 |

| 3.1    | The digital quadrature demodulator model                 | 18 |

| 3.2    | Simulating the demodulator with individual error sources | 21 |

| 3.3    | Simulating the complete demodulator                      | 27 |

| 3.4    | Summary                                                  | 32 |

| 4 De   | esign and implementation of the prototype                | 33 |

| 4.1    | Dacs in context of radar architecture                    | 33 |

| 4.2    | Statement of key user requirements                       | 34 |

| 4.3    | System design                                            | 35 |

| 4.4    | Hardware design and implementation                       | 35 |

| 4.5    | Programmable logic design and implementation             | 38 |

| 4.6    | Software design and implementation                       | 42 |

| 4.7    | Measuring the performance of the demodulator prototype   | 44 |

| 4.8    | Summary                                                  | 51 |

| 5 Su   | ımmary                                                   | 54 |

| 5.1    | Analysis of results                                      | 54 |

| 5.2    | Summary                                                  | 56 |

| 5.3    | Conclusions                                              | 57 |

| 5.4    | Recommendations                                          | 57 |

| A Si   | mulation of the demodulator                              | 59 |

| A.1   | Digital quadrature demodulator model |    |  |  |

|-------|--------------------------------------|----|--|--|

| A.2   | Simulation parameters                | 59 |  |  |

| В Мі  | icrocontroller software tools        | 61 |  |  |

| B.1   | Software libraries and tools         | 61 |  |  |

| B.2   | Cross-compiling the software         | 61 |  |  |

| B.3   | Programming the flash memory         |    |  |  |

| C Tes | sting the hardware and software      | 63 |  |  |

| C.1   | Hardware tests                       | 63 |  |  |

| C.2   | Firmware tests                       | 64 |  |  |

| C.3   | Software tests                       | 65 |  |  |

| Bil   | bliography                           | 66 |  |  |

# **List of Figures**

| I  | Inputs and outputs of the digital quadrature demodulator                                        | . I |

|----|-------------------------------------------------------------------------------------------------|-----|

| 2  | Block diagram of the Dacs board                                                                 |     |

| 3  | Stepped frequency continuous radar waveform                                                     | . 4 |

| 4  | Architecture of the Venus SFCW radar system                                                     | . 5 |

| 5  | Signal flow in the digital quadrature demodulator                                               | . 6 |

| 6  | Errors in the I and Q components translate into amplitude and phase errors                      | . 8 |

| 7  | The clock edge associated with the sample s[0] is ambiguous                                     | . 8 |

| 8  | High-level block diagram of the demodulator                                                     | 10  |

| 9  | Aperture delay introduces an error into the sampled voltage                                     | 13  |

|    | Block diagram of the demodulator model                                                          |     |

| 11 | Simulated rms amplitude error versus coherent integration factor for 14-bit quantizer           | 22  |

| 12 | Simulated rms phase error versus coherent integration factor for 14-bit quantizer               | 22  |

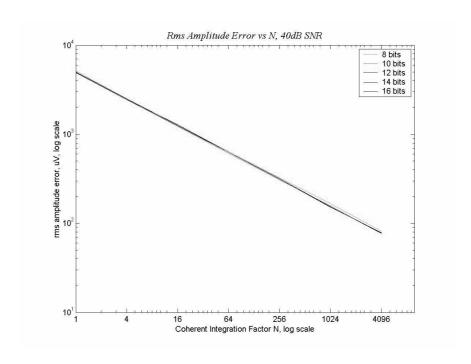

| 13 | Simulated rms amplitude error versus coherent integration factor for SNR=40 dB                  | 23  |

| 14 | Simulated rms phase error versus coherent integration factor for SNR = 40 dB                    | 23  |

| 15 | Simulated rms amplitude error versus coherent integration factor for SNR=80 dB                  | 25  |

| 16 | Simulated rms phase error versus coherent integration factor for SNR=80 dB                      | 25  |

| 17 | Simulated rms amplitude error versus coherent integration factor for 10-bit quantizer           | 26  |

| 18 | Simulated rms phase error versus coherent integration factor for 10-bit quantizer               | 26  |

| 19 | Simulated rms amplitude error versus N for $\sigma_j = 1x10^{-9}$                               | 28  |

| 20 | Simulated rms phase error versus N for $\sigma_j = 1x10^{-9}$                                   | 28  |

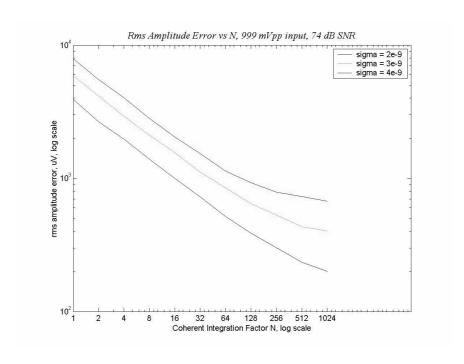

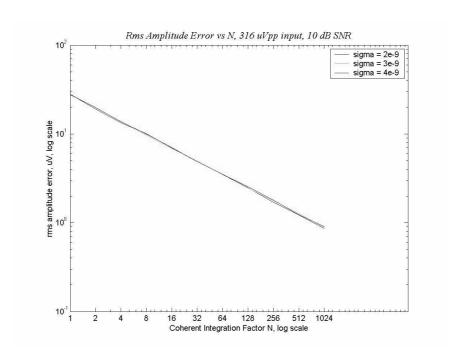

| 21 | Simulated rms amplitude error; amplitude = 999 mV <sub><math>pk-pk</math></sub> and SNR = 74 dB | 30  |

| 22 | Simulated rms phase error; amplitude = 999 mV $_{pk-pk}$ and SNR = 74 dB                        | 30  |

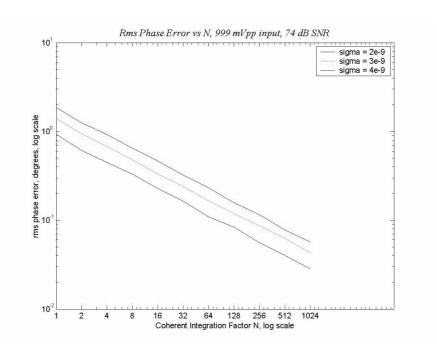

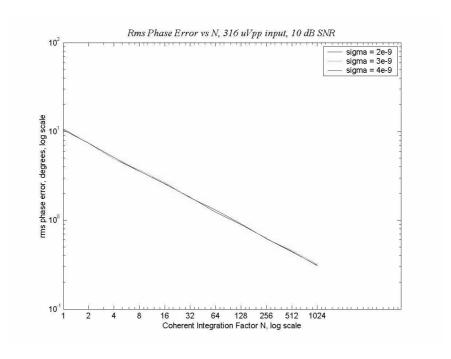

|    | Simulated rms amplitude error; amplitude = 316 $\mu$ V $_{pk-pk}$ and SNR = 10 dB               |     |

| 24 | Simulated rms phase error; amplitude = 316 $\mu$ V $_{pk-pk}$ and SNR = 10 dB                   | 31  |

| 25 | Architecture of the Venus radar system                                                          | 33  |

| 26 | Function blocks of the data capture system                                                      | 36  |

| 27 | Block diagram of the Dacs hardware                                                              | 36  |

|    | Block diagram of the VHDL code for the FPGA                                                     |     |

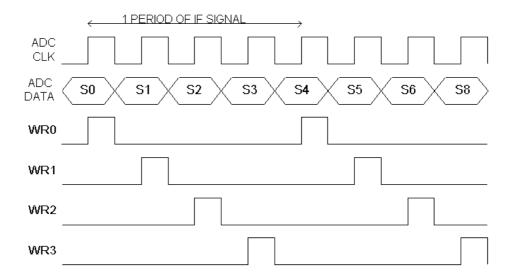

|    | Timing of accumulator write signals                                                             |     |

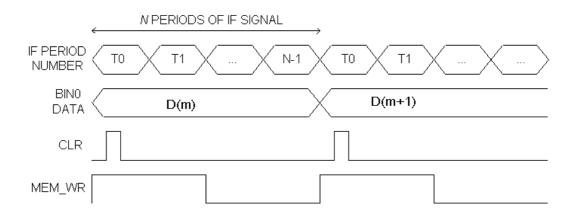

|    | Timing of the accumulator clear and memory write signals                                        |     |

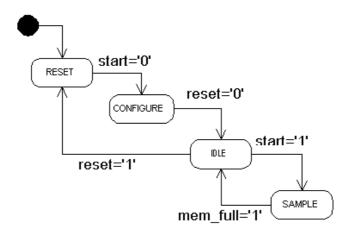

|    | State machine representation of the FPGA system controller                                      |     |

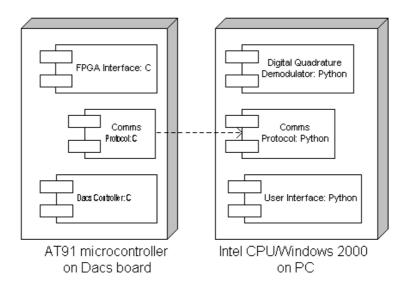

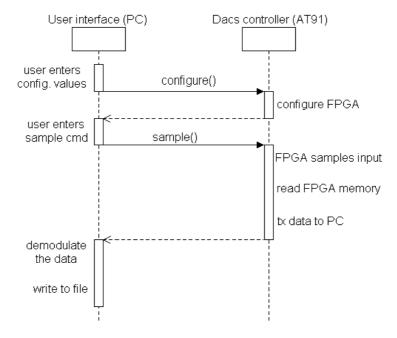

|    | Software is partitioned between the AT91 microcontroller and a PC                               |     |

|    | Sequence of software cooperation between PC and microcontroller                                 |     |

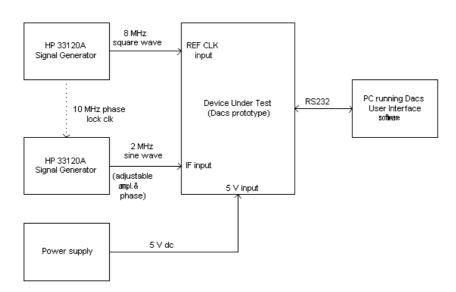

|    | Diagram of the test setup, showing clock frequency for subsampling inactive                     |     |

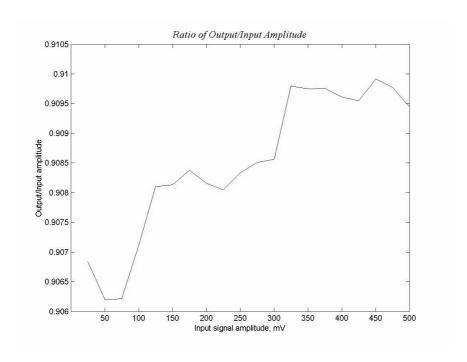

|    | Ratio of demodulator output amplitude to input signal amplitude                                 |     |

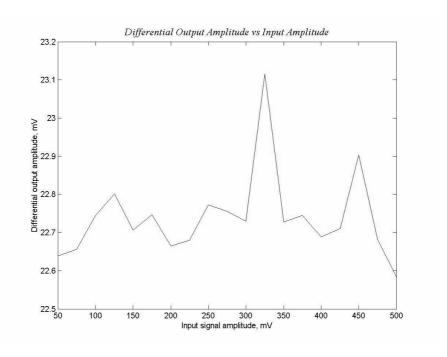

|    | Difference in output amplitude between consecutive input amplitude steps                        |     |

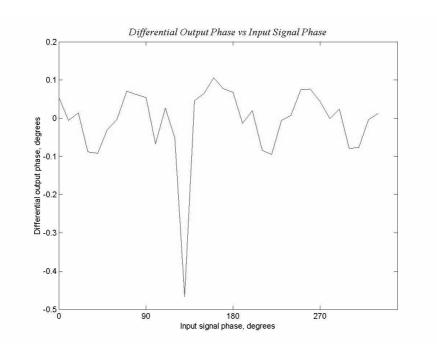

|    | Difference in phase output step size between consecutive phase steps                            |     |

|    | Measured rms amplitude error versus coherent integration factor                                 |     |

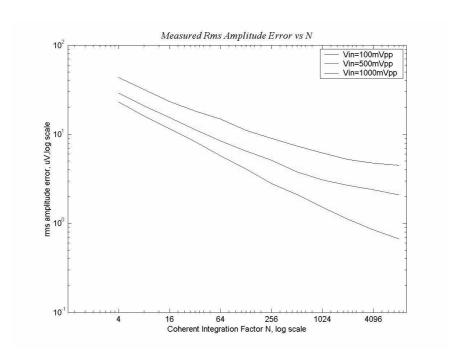

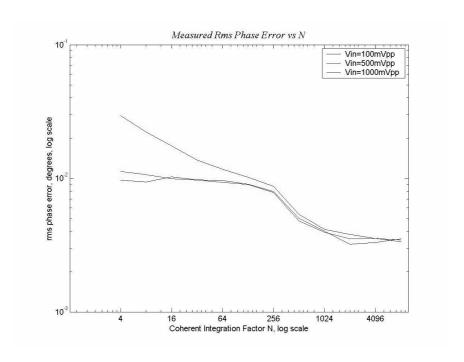

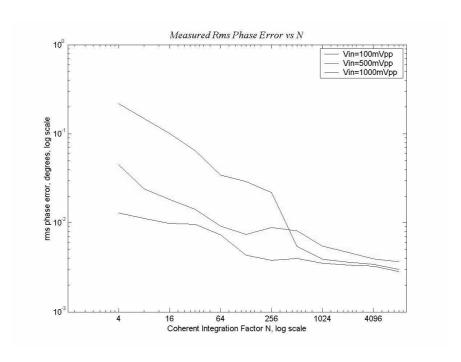

|    | Measured rms phase error versus coherent integration factor                                     |     |

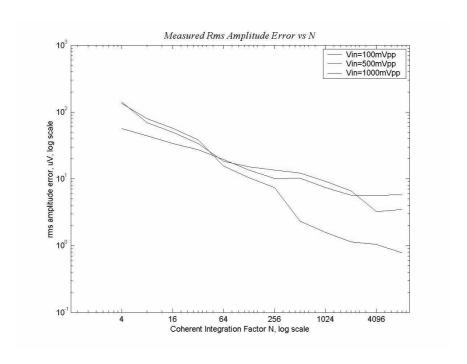

|    | Rms amplitude error versus coherent integration factor, for $P=5$                               |     |

|    | Rms phase error versus coherent integration factor, for $P=5$                                   |     |

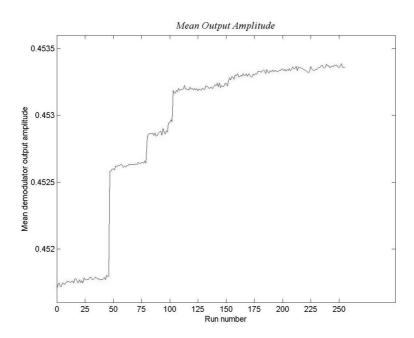

| 42 | Mean output amplitude of 256 ensembles, $N=1$                                                   | 64  |

#### viii

# **List of Tables**

| 1 | Threshold SNR and quantization noise floor against number of bits                  | . 24 |

|---|------------------------------------------------------------------------------------|------|

| 2 | Simulated rms errors for 40 dB SNR                                                 | . 27 |

| 3 | Rms error values for input amplitude of 499 mV and timing jitter std. dev. of 3 ns | . 29 |

| 4 | Rms error values for input amplitude of 158 uV and timing jitter std. dev. of 3 ns | . 32 |

| 5 | Effect of coherent integration on amplitude error for different input amplitudes   | . 49 |

| 6 | Effect of subsampling on amplitude error                                           | . 51 |

|   | Effect of subsampling on phase error                                               |      |

|   | Simulated performance compared to specifications                                   |      |

|   | Measured performance compared to specifications                                    |      |

# **Chapter 1 Introduction**

#### 1.1 Summary

The scope of this MSc project is the design and implementation of a *digital quadrature demodulator* for a new ground penetrating radar, known as Venus, which is an upgrade of an existing radar, MercuryB [1]. The demodulator is one module of the data capture system, abbreviated to *Dacs*, which is also responsible for controlling the radar and communicating with external computers.

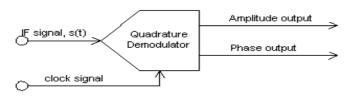

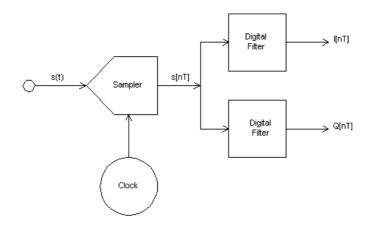

Figure 1. Inputs and outputs of the digital quadrature demodulator

A model of the quadrature demodulator was developed from the literature, and was simulated using the Monte Carlo technique. The simulations estimated the contribution of various error mechanisms and gauged the effectiveness of coherent integration in improving the accuracy of the demodulator output. Demodulator performance in the radar system was predicted by simulation.

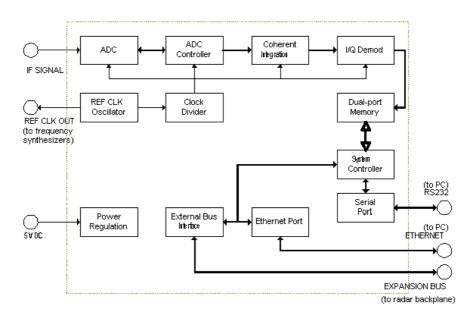

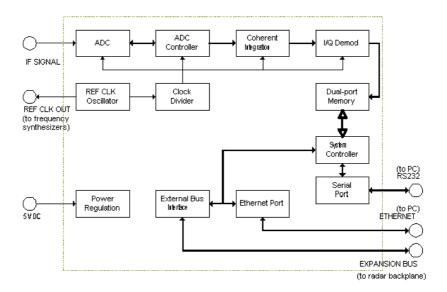

A working prototype was produced; Figure 2 is a system block diagram. The prototype demodulator performance was tested, and found to satisfy the specifications, although the signal generators used in the tests limited the precision of the results.

The most significant conclusion is that phase noise in the radar receiver's IF signal limits the demodulator accuracy, which exceeds the specified error allowance.

#### 1.2 Ground penetrating radar research at UCT

Ground penetrating radar (GPR) is a sensing technique that uses electromagnetic energy to produce an image of an underground target area [2]. The radar is usually in close contact with the earth's surface, looking into the ground, or it may be placed in a borehole or mineshaft. Ground penetrating radar is commonly used in landmine detection, mining, civil engineering, and archeology [2][3].

Figure 2. Block diagram of the Dacs board

The Radar Remote Sensing Group (RRSG) at the University of Cape Town began researching ground penetrating radar in 1988 [4], and has developed a radar system using a stepped frequency continuous wave architecture, housed in a portable enclosure [1][5]. The current version of this radar system is designated MercuryB, and is to be superceded by a new, upgraded design, Venus. The Dacs board, containing the digital quadrature demodulator, is one module of this radar.

The MercuryB radar hardware has a modular design, with synthesizer modules operating over the bands 200 to 1,600 MHz [1] and 800 to 3,200 MHz. A PC, communicating with the radar over a fibre-optic data link, acts as an operator interface, allowing for configuration of the the radar, measurement capture, and processing, display, and storage of the captured data. The radar data can be distributed over a network: observers at remote stations can receive the data stream for individual processing and interpretation [6].

The suitability of the MercuryB GPR system for various applications, such as surveying buried civil engineering structures and detection of non-metallic landmines has been examined in several field trials [1].

#### 1.3 Dissertation outline

This dissertation describes two related work areas: the design, construction, and testing of the new Dacs circuit board, and the development and simulation of a theoretical model of the digital quadrature demodulator.

Chapter 2 is the literature review and shows the top-down development of a *behavioural model* for the digital quadrature demodulator. The demodulator is placed in the context of the Venus stepped frequency continuous wave radar system, emphasizing the measurement of relative phase using two time-interleaved channels. A simple architecture for a digital quadrature demodulator that exploits the SFCW waveform is shown, then the implementation of the demodulator using real components is examined. Coherent integration is examined as a technique to improve the demodulator accuracy.

Chapter 3 discusses the simulation of the demodulator model using the Monte Carlo technique. The significant contributors to demodulator error are examined individually and their effect on the output error estimated; the potential improvement available through coherent integration is assessed. The model parameters are then set to match the prototype demodulator and the actual radar signals. Simulations using this model predict the performance of the demodulator in the radar system.

Chapter 4 is an overview of the design and development of the circuit board, programmable logic, and software, and begins with a brief requirements analysis. The chapter then shows the conceptual design of the data capture system, and concisely explains the design of the hardware, programmable logic, and software. The results of performance tests on the demodulator complete the chapter - the imprecision of the signal generators limited the value of these tests.

The final chapter presents an analysis of the simulations and measurements of the prototype demodulator performance. Simulations of the demodulator in the radar system show that phase noise in the IF signal causes the demodulator error to exceed the specified limits. The measurements demonstrate achieved performance within the tolerable limits, although the test signals had lower phase noise than the radar IF signal. A brief summary of the main results is followed by the conclusions and recommendations for future work.

Appendix A shows the derivations of some of the simulation parameters, and lists the parameters used for each series of simulations. Appendix B explains the tools used to compile the microcontroller software and program the flash memory on the prototype. Appendix C describes the tests performed on the prototype hardware, software, and programmable logic.

# Chapter 2 Literature review: digital quadrature demodulation

This chapter is an overview of the literature relevant to the design and implementation of a digital quadrature demodulator for a stepped frequency continuous wave radar system, and focusses on digitisation of the IF signal and the attendant imperfections.

#### 2.1 Architecture and operation of SFCW radar systems

#### 2.1.1 Stepped frequency continuous wave radar

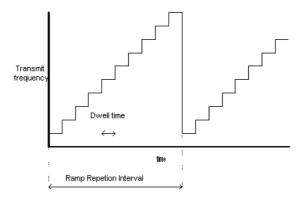

The stepped frequency waveform consists of a sequence of discrete, usually equally-spaced frequencies, each transmitted for a fixed time, known as the dwell time,  $T_{dwell}$  [7]. The ramp repetition interval is simply the number of frequency steps n multiplied by the dwell time.

Figure 3. Stepped frequency continuous radar waveform

One method for the stepped frequency processor to construct a synthetic range profile is by performing an inverse Fast Fourier Transform on the received waveform [8]. The synthetic range profile is similar to the range display produced by conventional pulse radars.

#### 2.1.2 The Mercury and Venus SFCW ground penetrating radar systems

The Venus radar was under construction at the time of writing, so this dissertation will refer to its predecessor, Mercury, as the same principles apply to both radars. The Mercury ground penetrating radar system detects the SFCW pulse using a heterodyne receiver [5]. The received

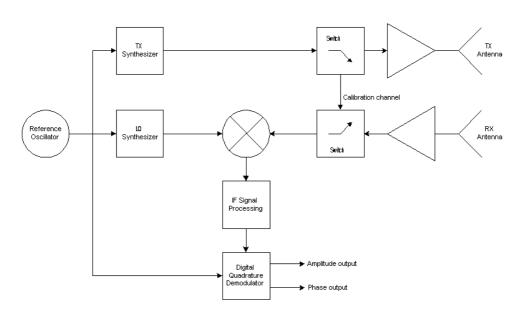

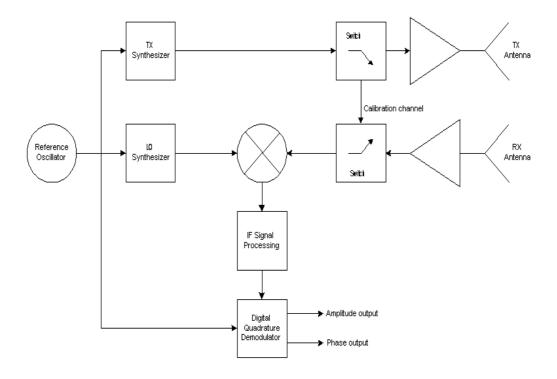

Figure 4. Architecture of the Venus SFCW radar system

signal is downconverted by mixing it with the local oscillator (LO) signal, producing an intermediate frequency (IF) signal at 2 MHz, with a bandwidth of 100 kHz [5].

The transmit frequency of the Mercury radar ranges from 200 to 1,600 MHz, or 800 to 3,200 MHz, depending on which synthesizer modules have been installed [1]. The RF components used in the transmitter and receiver do not have linear amplitude and phase responses over the operating bandwidth, corrupting the synthetic range profile [5]. The problem is solved by employing a time-interleaved heterodyne architecture: there is an extra channel between the transmitter and receiver. The signal through this extra channel contains the same corruptions as the signal through the transmit-receive channel, and is used as a calibration signal, allowing the amplitude and phase nonlinearities in the received signal to be removed [5]. The time interleaving is implemented by switches, as shown in Figure 4.

#### 2.2 Digital quadrature demodulation

Traditional demodulation schemes derive the in-phase and quadrature (I and Q) components by demodulation to baseband by two oscillator signals separated by  $\frac{\pi}{2}$  rad (i.e. in quadrature); each IF signal is then filtered individually and sampled by a separate ADC [9]. The components of the two channels are not perfectly matched and introduce an *imbalance* between the channels, which can cause phase errors as high as 2 to 3 degrees [10]. In direct digital demodulation, however, the downconverted carrier signal is digitised at a rate exceeding the Nyquist rate, after which the

digital signal is demodulated by two digital filters. The channel imbalances no longer exist, since the I and Q channel samples pass through the same analogue components [11].

#### 2.2.1 Architecture of a simple digital quadrature demodulator

Figure 5. Signal flow in the digital quadrature demodulator

A simple system for digital quadrature demodulation of a modulated carrier signal is shown in Figure 5 [12]. The carrier signal has been mixed down to a suitable intermediate frequency,  $\omega_{IF} = 2\pi f_{IF}$ . We write the intermediate-frequency signal as

$$s(t) = A(t)\cos(\omega_{IF}t + \phi) \tag{1}$$

$$= I(t).\cos(\omega_{IF}t) - Q(t).\sin(\omega_{IF}t)$$

(2)

where

$$I(t) = A(t).\cos(\phi t) \tag{3}$$

$$Q(t) = A(t).\sin(\phi t) \tag{4}$$

are the in-phase and quadrature components respectively [12]. We now digitise the IF signal s(t) by sampling at  $f_s = 4f_{IF}$ . Considering one period, this gives us a digital signal, s[n], which is s(t) sampled at

$$t = \frac{n\pi}{2} \quad ; n = 0, 1, 2, 3 \tag{5}$$

Digital filters process the sample sequence s[n] to give the I and Q components [12]:

$$I(t) = s[0] - s[2] (6)$$

$$Q(t) = s[3] - s[1] (7)$$

The amplitude and phase of the carrier signal are then just

$$A(t) = \sqrt{I(t)^2 + Q(t)^2}$$

(8)

$$\phi(t) = \arctan\left(\frac{Q(t)}{I(t)}\right)$$

(9)

Since the amplitude A(t) and phase offset  $\phi(t)$  of the IF signal are constant during each frequency step in the SFCW waveform, we will denote them as the constants A and  $\phi$  for convenience.

#### 2.2.1.1 Sampling errors introduce inaccuracies into the demodulator outputs

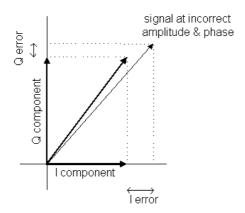

The sample sequence s[n] in a real system contains errors since the electronic components employed are imperfect. We therefore introduce time-varying error terms  $\epsilon_I(t)$  and  $\epsilon_Q(t)$  into the in-phase and quadrature components derived from these samples, writing the components as  $I'(t) = I + \epsilon_I(t)$  and  $Q'(t) = Q + \epsilon_Q(t)$  respectively, where I and Q are the ideal values, so that the demodulator amplitude and phase outputs are given by

$$A'(t) = \sqrt{(I + \epsilon_I(t))^2 + (Q + \epsilon_Q(t))^2}$$

(10)

$$\phi'(t) = \arctan\left(\frac{Q + \epsilon_Q(t)}{I + \epsilon_I(t)}\right)$$

(11)

and now contain errors that change with time; Figure 6 depicts this as a vector diagram. It is easily seen that the significance of the errors depends on the amplitude of the input signal: error terms  $\epsilon_I$  and  $\epsilon_Q$  of a given magnitude will cause greater inaccuracies for smaller signal amplitudes. It is also worth noting that the sensitivity of the phase output depends on the input phase, in particular on the ratios  $\frac{\epsilon_I}{I}$  and  $\frac{\epsilon_Q}{Q}$ .

Figure 6. Errors in the I and Q components translate into amplitude and phase errors

#### 2.2.2 Measuring the phase of the IF signal

The Mercury SFCW radar system has a 16 MHz oscillator which provides the reference for both the transmit and local-oscillator frequency synthesizers (abbreviated TXS and LOS respectively) and the quadrature demodulator. The IF signal, produced by mixing the received signal with the LO signal, is at a center frequency of 2 MHz. Quadrature demodulation requires a sampling frequency  $f_s$  to be four times the input frequency  $f_{in}$ : the reference oscillator is divided down to produce the 8 MHz sampling clock.

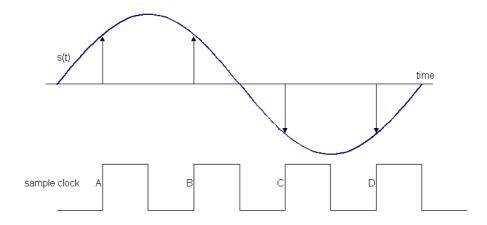

Figure 7. The clock edge associated with the sample s[0] is ambiguous

There are four clock edges per input signal period (Figure 7), and the choice of reference edge

is arbitrary, but the output phase depends on the reference edge choice. The problem is avoided by a fortunate result of the interleaved architecture: measuring the *relative* phase difference between the calibration and transmit-receive channels means the arbitrary reference edge is the same for both channels. Although the absolute phase values may change by a multiple of  $\frac{\pi}{2}$  rad after a power-cycle, the relative phase difference remains constant.

#### 2.2.3 Coherent integration improves demodulator performance

Coherent integration is the averaging of an ensemble of observations of a noisy signal with the same expected value, and reduces the *noise power* [13]. The variance of the noise signal,  $\sigma_1^2$ , is reduced by the factor N when successive observations are uncorrelated:

$$\sigma_N^2 = \frac{\sigma_1^2}{N} \tag{12}$$

where  $\sigma_N^2$  is the variance of the noise signal after coherent integration over ensemble length N [13]. Since the signal-to-noise ratio of a sinusoid in the presence of white noise is simply the signal variance over the noise variance [14], the signal-to-noise ratio is also improved by the factor N. The standard deviation of the noise, or how far the *noise voltage* deviates from the mean, is only reduced by a factor of  $\sqrt{N}$ .

This "one-upon-N" rule does not hold for time averages in systems where the sampling rate is high enough to avoid aliasing, since the noise in successive observations is then correlated to some extent [13] - the variance  $\sigma_N^2$  tends towards  $\sigma_1^2$  as the sample-to-sample correlation of the noise increases.

#### 2.2.4 Subsampling reduces the sampling rate

All four samples required for quadrature demodulation are usually taken in one period of the input waveform at a sample rate of  $f_s = 4f_{in}$ . Subsampling arises from the simple observation that the sampling points occur at identical phases in each period, and will therefore have identical values if the input signal is periodic, allowing the use of a lower sampling frequency and a cheaper ADC [1]; the penalty is that the samples must be taken over several periods of the input waveform. The actual sampling frequency required for subsampling is

$$f_{actual} = \frac{4f_{in}}{P} \tag{13}$$

where  $P = 3, 5, 7, \dots$  is the number of periods.

The prototype demodulator was constructed with an ADC capable of sampling at 8 MSa/s, so

subsampling is superfluous. The demodulator model is independent of the *sampling* frequency, and predicts that subsampling offers no performance improvement; this claim was verified empirically (Section 4.7.3.4.)

#### 2.3 Modelling the digital quadrature demodulator

The digital quadrature demodulator is implemented using analogue and mixed-signal circuitry to digitise the input and digital logic to process the samples. Numbers in a sampled-data system are represented with finite precision, which can introduce errors due to truncation or rounding [15]; the word length in this application is sufficient that these errors are negligible in comparison to errors introduced in sampling; only multiplication (by a power of 2) is performed on the FPGA; the 32-bit results are converted to floating-point representation on a PC and then divided.

#### 2.3.1 Top-level model of the demodulator

Figure 8. High-level block diagram of the demodulator

The demodulator structure is shown as a block diagram in Figure 8. The model for each analogue or mixed-signal component is expanded below; the coherent integration and quadrature demodulation operations are implemented digitally.

#### 2.3.1.1 Approaches to modelling the analogue-to-digital converter in the demodulator

There is an extremely large body of literature on analogue-to-digital conversion, stretching as far back as the realisation that pulse-code modulation was in effect digitisation [16]. An important category within this literature is concerned with modelling ADCs and their error mechanisms. Aimed at chip *designers*, these papers generally produce analytical descriptions of

the converter. As ADCs become more and more integrated, including large amounts of digital circuitry, modelling and simulating the chip in analogue simulation programmes becomes very time-consuming [17]. One solution is to model the *behaviour* of the components in the time domain, using statistical descriptions for random phenomena. ADCs have been modelled and simulated in languages from Matlab [18], [19], [20] to AHDL and even VHDL [17], a language designed for describing digital logic.

Correction of systematic converter errors by processing the ADC output data is also a well-covered topic. A common approach is to model the ADC as an ideal converter with an error source described by a dynamic error function [21]. An error correction algorithm or table is programmed using parameters obtained from calibration, and then used to remove errors from the ADC output. No *a priori* knowledge of the converter structure is assumed.

The primary purpose of the following sections is to investigate the error mechanisms and how they affect the demodulator. This leads to a simplified model using a combination of analytical and behavioural descriptions in the time domain. The model is also independent of the converter architecture, useful since little information was available for the THS1408 selected for the prototype. Although modelling the demodulator and converter at an abstract level sacrifices some accuracy in predicting performance, the omitted errors are relatively small - the most significant sampling errors are caused by aperture jitter and thermal noise [22], which are included in the model.

#### 2.3.2 Thermal noise in the input signal

Real devices introduce thermal noise into signals. The received radar signal is already noisy, and processing by the downconverter introduces more thermal noise [5].

#### 2.3.2.1 Modelling thermal noise

Thermal noise  $s_{th}(t)$  is modelled as a band-limited, Gaussian noise process having flat power spectral density, zero mean, and constant variance  $\sigma_{th}^2$  - that is, as white noise. This is an adequate model for many significant noise sources in RF circuits [23]. The noise signal is superimposed on the ideal sinusoidal signal; the signal quality is indicated by the signal-to-noise ratio:  $SNR_{th} = 10 \log(\frac{P_s}{P_n})$  in decibels, where  $P_s$  and  $P_n$  are the signal and noise powers respectively [14].

#### 2.3.3 RF transformer

The single-ended IF signal is converted into a differential signal by an RF transformer. We

simplify the demodulator model by representing the transformer as a single-ended component, modelling it as an ideal opamp representing the insertion loss (i.e. the gain is less than unity.)

#### 2.3.4 Differential amplifier with programmable gain

The signal chain contains a differential amplifier with programmable gain, but this analysis will assume a constant gain setting. Opamp gain depends on frequency, but the input signal is at a constant frequency so the differential amplifier should have constant gain.

#### 2.3.4.1 Model of the amplifier

Opamps generally have internal frequency compensation networks to ensure stability over the whole range of input frequencies, although these limit the rate at which the output can slew [24]; the minimum slew rate needed for a sinusoid of amplitude A and frequency  $f_{in}$  is  $r_{slew} = 2\pi A f_{in}$  [24], giving a minimum requirement for this application of  $25V/\mu s$ . Although the THS1408 datasheet does not specify the slew rate, a survey of recent PGA datasheets suggests that the opamp slew rate will not be a serious limitation - the slew rate of the AD603 PGA is at least  $275V/\mu s$  [25], and Maloberti et al. use a slew rate of over  $1000V/\mu s$  in their simulations [20].

The amplifier adds thermal noise to its output signal - this converter model refers all thermal noise to the input signal for simplicity, so the amplifier will be considered noiseless. Other errors are assumed to be either neglible or - especially gain and offset errors - removed through compensation [26][27]. The differential amplifier is represented as a single-ended component with fixed gain  $G_a$  and offset  $v_{os}$  set to 0.

#### 2.3.5 Sample-and-hold circuit

Analogue-to-digital converters sample the input at regular intervals and then quantize the sampled voltage (supposedly held constant by the SNH.)

#### 2.3.5.1 Model of the sample-and-hold circuit

The sample-and-hold model described here is a vastly simplified version, consisting of an ideal sample-and-hold with aperture jitter [28]. It excludes classic sources of dynamic error such as droop, limited slew rate, and feedthrough [29]. The limited slew rate of sample-and-hold circuits causes errors that worsen with increasing input frequency, but this is no longer a significant limitation in recent ADC designs [30].

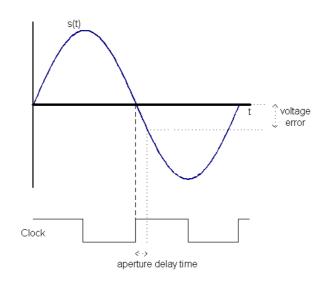

**Aperture delay and aperture jitter** In an ideal sample-and-hold circuit the input will be sampled exactly on the rising edge of the clock. But practical converters have a small delay from the clock edge to the time the input is completely disconnected from the hold capacitor.

The average delay is called aperture delay, or aperture time [31]. Power supply induced noise and variation of digital thresholds by thermal noise cause aperture jitter, which is cycle-to-cycle variation in the aperture delay; power supply noise can be effectively eliminated by judicious filtering [28]. Aperture delay and aperture jitter cause the sampling instant to deviate from the ideal and thereby introduce an amplitude error into the sampled voltage (Figure 9.)

Figure 9. Aperture delay introduces an error into the sampled voltage

Modelling aperture delay and jitter Aperture delay  $\epsilon_{aj}(t)$  is modelled as a stationary Gaussian random process with the mean corresponding to the aperture delay and a small variance corresponding to the aperture jitter. The delay is effective from the rising edge of the clock signal. The input signal is sampled at instants  $t = nT_s + \epsilon_{aj}(t)|_{t=nT_s}$  where n = 0, 1, 2, ... and  $T_s$  is the clock period. The aperture delay is of course the same when the calibration and transmit/receive channels of the radar are selected; we are interested in measuring *relative* phase difference between the channels, and so set the mean delay to zero.

#### 2.3.5.2 The effect of aperture delay and jitter on sampling

Kobayashi et. al. consider the case where a sinusoidal input  $s(t) = A \sin(2\pi f_{in}t)$  is sampled at time  $t = nT_s + \epsilon_{aj}(t)$ , where  $T_s$  is the sampling period and  $\epsilon_{aj}(t)$  is the aperture jitter, assumed to follow a Gaussian distribution with zero mean and a standard deviation of  $\sigma_{aj}$ . The amplitude error due to aperture jitter is then

$$\Delta V_{aj} \approx \epsilon_{aj}(t) \frac{ds(t)}{dt} |_{t=nT_s}$$

(14)

which has a maximum when the sampling instant occurs at a zero-crossing, where the input slope is maximum, giving

$$\Delta V_{aj} \approx \epsilon_{aj}(t) A 2\pi f_{in} \tag{15}$$

where it is assumed that  $2\pi f_{in}\sigma_{aj} << 1$  [32] [33].

#### 2.3.6 Clock oscillator and timing jitter

An oscillator is an autonomous system producing a periodic output,  $s_{osc}(t)$ : an ideal oscillator's output depends only on time, but random events (noise) in real oscillators perturb the oscillator output, causing phase and amplitude deviations [34]. A sampled-data system using a square-wave oscillator output as its clock signal experiences these deviations as timing jitter: the transitions of the sampling clock occur at times deviating from the ideal. Timing jitter is exacerbated by mechanisms other than oscillator phase noise when the clock signal is passed through digital logic. In particular, the finite rise-time of logic signals and unstable digital logic thresholds worsen the jitter experienced at the sample-and-hold clock input [35].

#### 2.3.6.1 Modelling timing jitter

One can write the oscillator output, including the phase and amplitude disturbances, as

$$s_{osc}(t + \alpha(t)) + y(t) \tag{16}$$

where  $\alpha(t)$  is the phase deviation, and y(t) is the amplitude deviation [36].

The amplitude deviations y(t) are small and transient, and are compensated for by amplitude limiting mechanisms in the oscillator itself [37] - these deviations are therefore negligible and will be ignored.

The phase deviation  $\alpha(t)$  is the most important effect of oscillator noise;  $\alpha(t)$  will, in general, keep increasing with time as the effect of the phase perturbations is cumulative [36]. Further,  $\alpha(t)$  is a Gaussian random variable with constant mean and a variance that increases linearly with time [36, p. 3]. The jitter variance of a square-wave oscillator therefore increases linearly with time as the oscillator output deviates further from the ideal the longer the oscillator runs [36]. In the quadrature demodulator, however, the input signal and the sampling clock are derived from the same oscillator, so the input and clock signals will only experience small, short-term phase

shifts, but will maintain a steady phase relationship over time. The delay between the received signal and the local oscillator signal is very short for ground penetrating radar, so the phase noise of the received signal is correlated with that of the LO signal [1]. Timing jitter is dependent on the target range: the received signal is delayed more for more distant targets, and the oscillator phase noise is integrated over a longer period of time, giving rise to worse jitter. The dependence of jitter on range was not explicitly examined.

Timing jitter can be derived from oscillator phase noise Timing jitter is the effect of oscillator phase noise observed in the time domain; the phase noise for a given oscillator is usually specified by a plot of single-sideband noise spectral density L(f) in the frequency domain. Noise spectral density can be integrated over a particular frequency range to obtain the phase noise power over the chosen bandwidth, from which the rms timing jitter can be calculated by treating it as the equivalent sideband power of a phase modulator [38].

**Model used for simulations** Timing jitter  $\epsilon_{tj}(t)$  was modelled as a Gaussian random variable with zero mean and constant variance, a reasonable approximation since the input and clock signals are derived from the same source. The standard deviation  $\sigma_j$  of the timing jitter was specified in units of time - typical values, gauged from the simulations performed by Maloberti et al., are standard deviations ranging from 1 to 10ns [20]. The effects of logic gate jitter are assumed to be allowed for by choosing a jitter variance larger than than that of the oscillator alone.

#### 2.3.6.2 The effect of timing jitter on sampling

Timing jitter introduces an amplitude error into the sampled value in exactly the same way as aperture jitter - the error can be calculated by substituting  $\epsilon_{tj}$  for  $\epsilon_{aj}$  in (15).

#### 2.3.7 Quantizer introduces quantization noise

The quantizer converts the analogue sample-and-hold output into a digital code: each code represents a unique reconstruction level. Since the quantizer has a fixed number of reconstruction levels and the input signal has an infinite number of possible values, the quantized output is necessarily an imperfect copy of the input signal.

#### 2.3.7.1 Model of a mid-tread uniform quantizer

The quantizer is modelled as an ideal quantizer, which can be defined as consisting of a set of contiguous intervals or cells on a partition of the real line. Each cell has a reproduction level or code, placed in the middle of the cell. The quantizer output is then simply the reproduction level or code closest to the input [16]. The transfer function is a staircase function when plotted on

Cartesian axes, and can be described mathematically as

$$q(x) = \left\{ \begin{array}{l} \left(\frac{M}{2} - 1\right) \Delta; \quad \left(\frac{M}{2} - 1.5\right) \Delta \leq x \\ k\Delta; \quad (k - 0.5) \Delta \leq x < (k + 0.5); \\ \left(-\frac{M}{2}\right) \Delta; \quad x < \left(-\frac{M}{2} + 0.5\right) \Delta \end{array} \right\}$$

where  $M$  is the number of reconstruction levels, and  $\Delta$  is the width of the reconstruction cells,

where M is the number of reconstruction levels, and  $\Delta$  is the width of the reconstruction cells, or the bin width, and the index k has the range  $k = \left(-\frac{M}{2} + 1\right), ..., \left(\frac{M}{2} - 2\right)$  [39].

Quantizers in real ADCs are clocked at the sampling frequency, so that the output code changes only on clock edges. In practice, the output code is represented as a binary word of width b bits, so the number of levels is  $M=2^b$ . A quantizer is *uniform* if the quantization levels are equally spaced, and is known as a mid-tread quantizer if a reconstruction level exists at exactly 0 volts, and each reconstruction level is a multiple of  $\Delta$  from the x-axis.

#### 2.3.7.2 Quantization noise

The quantizer error  $\epsilon_q$  is defined as  $\epsilon_q = Q(x) - x$ . The quantizer output is expressed as the sum of the input signal and the quantizer noise. Since the quantizer input is generally a sequence of samples x(n), the quantizer noise process is  $\epsilon_q[nT_s] = Q(x[nT_s]) - x[nT_s]$ , and is often characterised statistically [39].

**Quantization error in synchronous sampling causes spurious signals** The nominal ratio of signal to quantization noise is

$$SNR_{nom} = 6.02b + 1.76 \quad (dB)$$

(18)

where b is the number of quantizer bits [40]. Coherent sampling, or synchronous sampling, occurs when the ratio of the sampling frequency to the input frequency is an integer larger than 1 (i.e.  $f_s = mf_{in}$ ; m a natural number >1) [40]. The quantization error due to synchronous sampling is deterministic, and (18) no longer holds. The deterministic quantization noise causes spurious signals, observable in FFT plots of sampled data [40]; the quantization noise process is distinctly periodic, and can be described by a Fourier series for simple inputs [39]. The third harmonic will usually have the highest amplitude since it is the odd harmonic with the lowest order, especially when the input amplitude is low [41].

#### 2.3.7.3 Dithering improves data converter performance

Dithering is the addition of a random signal to the input of an ADC and can be achieved by simply averaging successive quantizer output values if the input signal already contains random noise- this is known as nonsubtractive dithering [42]. Dithering is implemented in this design

by coherent integration, which produces four averaged sample values for every N periods. The random signal is provided by the thermal noise in the input signal; Gaussian noise causes the quantization error to be approximately uniform even when the quantization step size  $\Delta$  is as large as the standard deviation of the noise [43].

**Dithering reduces quantization error** Dither can, in theory, reduce quantization error to a negligible quantity and minimize coherent signal spurs caused by the nonlinear quantizer transfer function, at the cost of reduced converter bandwidth [44]. In practice, however, dither usefully removes small-scale (i.e. localised) linearity errors, but large-scale errors must be removed by a look-up table or compensation algorithm [45].

Dithering reduces differential nonlinearity error The cell width  $\Delta$  varies slightly from code to code in practical converters, a property expressed by the differential linearity, the difference between each cell's actual width and the ideal value [46]; some codes are good and some codes are bad [30]. Differential nonlinearity causes spurious signals, which can be reduced by dithering, which effectively randomizes the errors so that the averaged output contains less error than if the input exercised only a bad code [30].

#### 2.4 Summary

SFCW radars produce a series of discrete tones, measuring the amplitude and phase of the received signal at each frequency step. The Mercury and Venus SFCW radars use a time-interleaved heterodyne architecture to compensate for errors in the RF components; this also removes the ambiguity in the sampled phase. A digital quadrature demodulator measures the radar IF signal amplitude and phase by sampling at twice the Nyquist rate and filtering the samples to produce estimates for the in-phase and quadrature components, avoiding the imbalances which plague analogue demodulation schemes.

The IF signal samples contain errors, causing inaccuracy in the demodulator outputs. Coherent integration promises to reduce the effect of random errors, at the expense of increased conversion time.

A model of the demodulator was produced for use in computer simulation of the demodulator performance. The model shows that thermal noise and clock jitter are the most significant sources of random errors in sampling; systematic errors can be compensated for, and are also attenuated by dithering, implemented in this case by coherent integration.

# Chapter 3 Simulating the digital quadrature demodulator

This chapter presents a behavioural model of the complete demodulator that includes analogue, mixed-signal, and digital components, and describes the simulations predicting the harmful effect of component errors on the demodulator outputs. These simulations assisted in defining the system design parameters (sampling rate, coherent integration factor.)

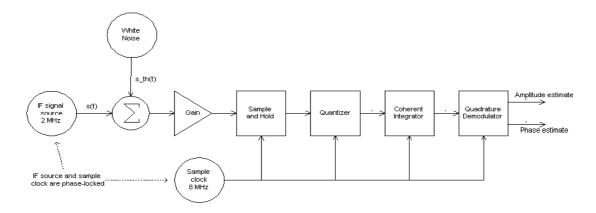

#### 3.1 The digital quadrature demodulator model

#### 3.1.1 Components of the model

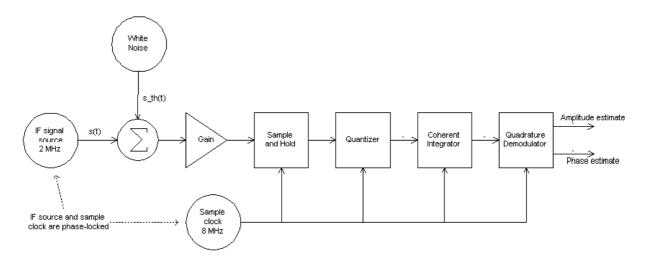

Figure 10. Block diagram of the demodulator model

The demodulator was simulated in the discrete-time domain, with timestep  $T_s$  equal to the clock period, 125 ns; the equations are written as functions of discrete time  $t_n$ , the timestep variable n ranging from 0 to  $N_{\rm max}$ .

#### 3.1.1.1 Oscillators

The 2 MHz oscillator is an ideal oscillator, with output

$$s[t_n] = A\cos(2\pi f_{in}nT_s + \phi)$$

;  $n = 0, 1, 2, ...N_{\text{max}}$

where A and  $\phi$  are the amplitude and phase parameters, and the frequency  $f_{in}$  is 2 MHz.

The 8 MHz clock oscillator is modelled as an ideal oscillator with random timing jitter, assumed to be Gaussian. Following the form used by Awad [47], we let the rising edges of the

clock signal occur at

$$t_{CLK}[t_n] = nT_s + \epsilon_i[n] ; n = 0, 1, 2, ...N_{\text{max}}$$

where the timing jitter  $\epsilon_j[n]$  is the jitter random variable associated with the *n*th sampling instant;  $\epsilon_j[n]$  are identical and independent Gaussian random variables with zero mean and a variance of  $\sigma_j^2$  [47].

#### 3.1.1.2 Gaussian white noise

The white noise signal  $s_{th}[t_n]$  is a Gaussian random process with zero mean and a variance of  $\sigma_{th}^2$ . The noise power is set directly by the signal-to-noise ratio,  $SNR_{th}$ , using the IF signal power as numerator (see Appendix A.)

#### 3.1.1.3 Gain

The transformer and amplifier were combined and modelled as a single gain,  $G_a$ :

$$s_a[t_n] = G_a(s[t_n] + s_{th}[t_n])$$

#### 3.1.1.4 Sample-and-hold

The sample-and-hold was an ideal sample-and-hold, and the output was calculated as the IF signal value at the sample time *including jitter*, including the noise voltage:

$$s_{snh}[t_n] = s_a[nT_s + \epsilon_j[n]]$$

=  $G_a(s[nT_s + \epsilon_j[n]] + s_{th}[t_n]) ; n = 0, 1, 2, ...N_{max}$

#### **3.1.1.5 Quantizer**

The quantizer was as an ideal midtread quantizer Q(x), with  $2^B$  reconstruction levels; the number of bits B and the quantizer range were specified as parameters. The quantizer output was

$$x_q[t_n] = Q(s_{snh}[t_n])$$

#### 3.1.1.6 Coherent integrator

The coherent integrator is simply nonsubtractive dithering implemented individually on the sample streams corresponding to each of the four sampling phases, with the coherent integration factor N as the ensemble length. The accumulator outputs after N periods are therefore

$$\begin{array}{lll} x_{acc0}[i] & = & (x_q[iNT_s] + x_q[(iN+4)T_s] + x_q[(iN+8)T_s] + \ldots)/N \\ \\ x_{acc1}[i] & = & (x_q[(iN+1)T_s] + x_q[(iN+5)T_s] + x_q[(iN+9)T_s] + \ldots)/N \\ \\ x_{acc2}[i] & = & (x_q[(iN+2)T_s] + x_q[(iN+6)T_s] + x_q[(iN+10)T_s] + \ldots)/N \\ \\ x_{acc3}[i] & = & (x_q[(iN+3)T_s] + x_q[(iN+7)T_s] + x_q[(iN+11)T_s] + \ldots)/N \end{array}$$

where the index i=0,1,2..L-1 is the number of completed sets of N sinewave periods, and L is a parameter specifying how many contiguous measurements (each requiring N periods) should be taken.

#### 3.1.1.7 Quadrature demodulator

The coherent integrator outputs are averaged sample values of the input signal at phases  $\Phi = \frac{k\pi}{2}$ ; k = 0, 1, 2, 3. The in-phase and quadrature components are calculated as an intermediate step (the voltages are referred to the demodulator input by dividing by the amplifier gain):

$$I'[i] = \frac{x_{acc0}[i] - x_{acc2}[i]}{2G_a}$$

(19)

$$Q'[i] = \frac{x_{acc3}[i] - x_{acc1}[i]}{2G_a}$$

(20)

The amplitude and phase outputs are then:

$$A'[i] = \sqrt{I'[i]^2 + Q'[i]^2}$$

(21)

$$\phi'[i] = \arctan\left(\frac{Q'[i]}{I'[i]}\right)$$

(22)

A complete simulation therefore produces L estimates for the amplitude and phase, respectively A'[i] and  $\phi'[i]$ , for each combination of parameters.

#### 3.1.1.8 Error signals

The simulation aims to investigate the *errors* in the demodulator outputs, so the amplitude and phase errors were recorded to file, for statistical analysis in Matlab. The error signals were calculated as

$$\epsilon_A[i] = A'[i] - A$$

$$\epsilon_{\phi}[i] = \phi'[i] - \phi$$

#### 3.1.2 Simulation in the time domain using Python

The time-domain behaviour of the demodulator model was simulated on computer using Monte Carlo techniques in Python, an open-source, interpreted language [48]. Each simulation run was specified by supplying a set of values for each parameter. The parameters were varied in sequence, such that L experiments were performed for each parameter combination. The errors show some dependency on the input phase, so more than one value for  $\phi$  was used; the mean of the rms error over the phases was taken, reducing the effect of input phase on the results.

#### 3.2 Simulating the demodulator with individual error sources

#### 3.2.1 Simulating thermal noise

Thermal noise was simulated in two phases: the first phase covered a wide set of parameters but used only one value for input phase  $\phi$  to reduce computation time; the second phase examined a narrower set of parameters in more detail, using 11 different  $\phi$  values (see Section A 2.1.)

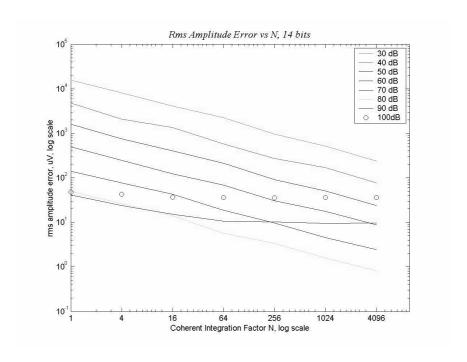

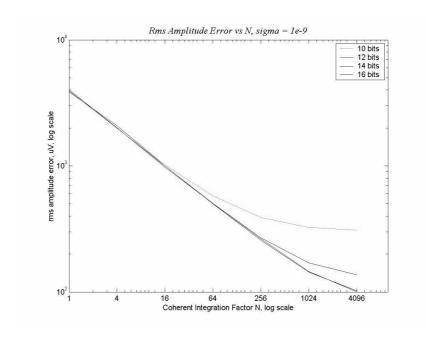

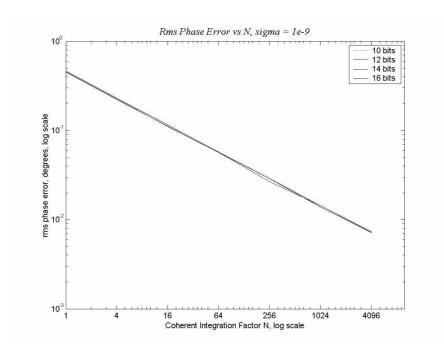

#### 3.2.1.1 Simulation results for a single phase value

Simulated rms amplitude and phase errors are shown in Figures 11 and 12 for a 14-bit quantizer. Coherent integration reduces the amplitude and phase errors by a constant ratio at lower signal-to-noise ratios; the error tends to an horizontal asymptote (typically for N>64) at a threshold SNR; and coherent integration has no effect at the highest signal-to-noise ratios. Random thermal noise and deterministic quantization noise respond differently to averaging: coherent integration reduces the error contribution of white noise, but, at as the SNR rises, the noise voltage becomes much smaller than the quantizer step size and dithering has no effect; the output error is now due to quantization alone and will not be removed by averaging.

Coherent integration starts to show diminishing returns at a threshold SNR roughly corresponding to the theoretical noise floor due to quantization noise, as per (18). The relationship is illustrated in Table 1. This happens when the additive noise starts to become too small to cause dithering; the noise standard deviation,  $\sigma_{th}$ , is about one-quarter of the quantizer step size at the threshold.

#### 3.2.1.2 Simulation results for several phase values

The second phase of the simulations used a larger set of input signal phase  $\phi$  values, resulting in a larger data set in which the effects of input phase could be averaged out.

Figures 13 and 14 show the simulated rms amplitude and phase error versus coherent

Figure 11. Simulated rms amplitude error versus coherent integration factor for 14-bit quantizer

Figure 12. Simulated rms phase error versus coherent integration factor for 14-bit quantizer

Figure 13. Simulated rms amplitude error versus coherent integration factor for SNR=40 dB

Figure 14. Simulated rms phase error versus coherent integration factor for SNR = 40 dB

| Quantizer Bits | Quant. Noise Floor | Threshold SNR   |

|----------------|--------------------|-----------------|

| 8              | -50 dB             | 50 dB           |

| 10             | -62 dB             | 60 dB           |

| 12             | -74 dB             | $\approx$ 75 dB |

| 14             | -86 dB             | 90 dB           |

| 16             | -98 dB             | 100 dB          |

Table 1. Threshold SNR and quantization noise floor against number of bits

integration factor N for an input signal-to-noise ratio of 40 dB. The error is independent of the quantizer step size, indicating that the error is caused by thermal noise.

The rms amplitude and phase error,  $\epsilon_A$  and  $\epsilon_\phi$  respectively, maintain a constant ratio of improvement as N increases logarithmically. The reduction in *standard deviation* of the additive noise predicted by (12) is  $\frac{\sigma_1}{\sigma_2} = \sqrt{\frac{N_2}{N_1}}$ , where  $\sigma_1$  and  $\sigma_2$  are at  $N_1$  and  $N_2$  respectively. The simulation results show  $\frac{\epsilon_1}{\epsilon_2} \approx \sqrt{\frac{N_2}{N_1}}$ , where the two rms error values,  $\epsilon_1$  and  $\epsilon_2$  are at  $N_1$  and  $N_2$  respectively (see Table 2). The root mean square of the variance of the amplitude and phase error ensembles also approximates the relationship predicted by (12), which is that the ratio of the two variances should equal to N.

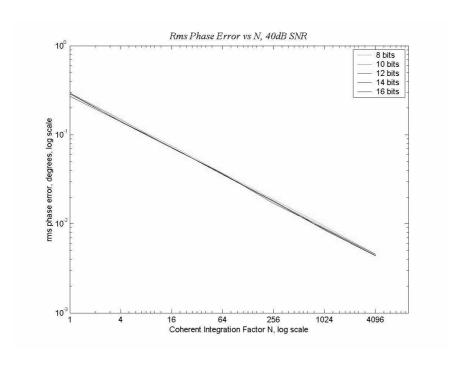

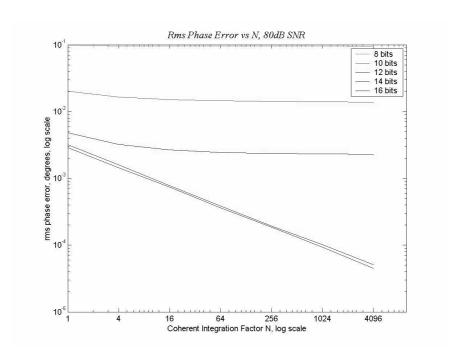

Figures 15 and 16 show the simulated rms amplitude and phase errors for an input signal-to-noise ratio of 80 dB. Coherent integration provides no improvement for 8-, 10-, and 12-bit quantizers, indicating the predominance of quantization noise. However, the errors for 14- and 16-bit quantizers are very similar, suggesting that random noise is here the deciding factor. This is confirmed by the constant ratio of improvement due to coherent integration. The additive noise here has a standard deviation of  $71\mu\text{V}$ , while the 14- and 16-bit quantizers have a maximum quantization error less than  $61\mu\text{V}$ . The results for 14 and 16 bits have the property that two rms error values,  $\epsilon_1$  and  $\epsilon_2$  at  $N_1$  and  $N_2$  respectively, have the ratio  $\frac{\epsilon_1}{\epsilon_2} \approx \sqrt{\frac{N_2}{N_1}}$ .

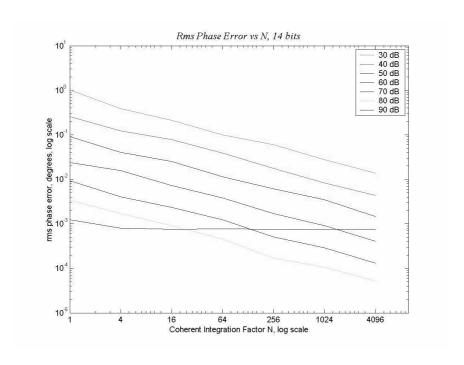

#### 3.2.2 Simulating timing jitter

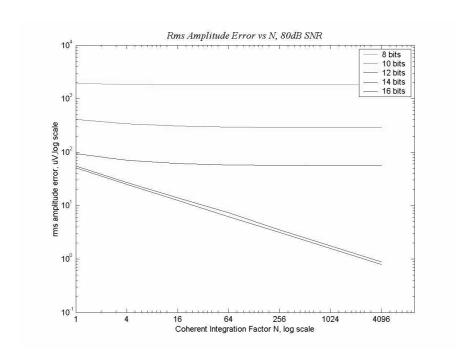

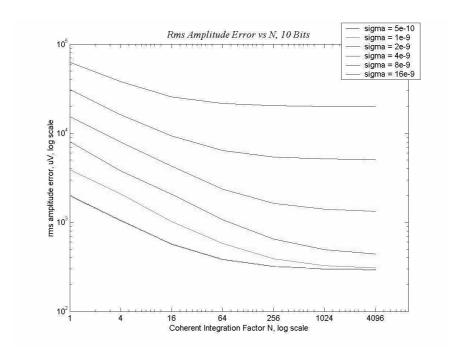

Figures 17 and 18 are log-log plots of the rms amplitude and phase error signals for a 10-bit quantizer, with separate curves for each  $\sigma_j$  value. The results for 12-, 14-, and 16-bit quantizers are similar. The severity of the errors is notable.

The most striking feature is the different effect of coherent integration on the amplitude and phase errors. The amplitude error tends towards an asymptote as N increases, especially for larger  $\sigma_j$  values. The phase error, however, maintains a constant ratio of improvement as N rises. The amplitude and phase are calculated from the same samples, so the difference in the error signals response to coherent integration must be explained by the demodulator equations. The

Figure 15. Simulated rms amplitude error versus coherent integration factor for SNR=80 dB

Figure 16. Simulated rms phase error versus coherent integration factor for SNR=80 dB

Figure 17. Simulated rms amplitude error versus coherent integration factor for 10-bit quantizer

Figure 18. Simulated rms phase error versus coherent integration factor for 10-bit quantizer

| В  | $\epsilon_{A,N=1}$    | $\epsilon_{\phi,N=1}$    | $var.of \ \epsilon_{A,N=1}$  | $var.of \ \epsilon_{\phi,N=1}$  |

|----|-----------------------|--------------------------|------------------------------|---------------------------------|

| _  | $\epsilon_{A,N=4096}$ | $\epsilon_{\phi,N=4096}$ | $var.of \epsilon_{A,N=4096}$ | $var.of \epsilon_{\phi,N=4096}$ |

| 8  | 63.3                  | 64.3                     | 4017                         | 4107                            |

| 10 | 63.8                  | 65.3                     | 4055                         | 4273                            |

| 12 | 64.4                  | 65.8                     | 4096                         | 4302                            |

| 14 | 63.7                  | 66.0                     | 4097                         | 4404                            |

| 16 | 64.0                  | 59.7                     | 4092                         | 3540                            |

Table 2. Simulated rms errors for 40 dB SNR

phase output is less sensitive at large input amplitudes.

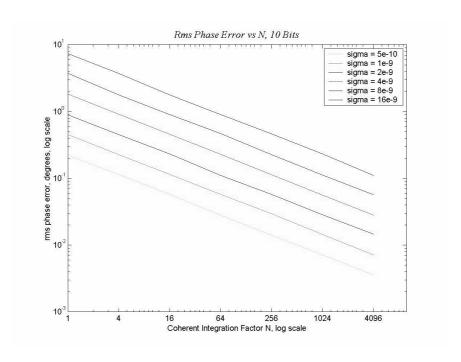

The rms amplitude and phase errors are proportional to the timing jitter (the relationship is clearer for larger N), clearly indicating that the error is caused by timing jitter, although the effects of quantization can be seen for low  $\sigma_j$  values. Plotting the results for different quantizers with constant  $\sigma_j$ , as in Figures 19 and 20, shows that the rms amplitude error is independent of quantizer step size, except at higher N in this case - the error is completely independent of quantizer step size for larger timing jitter. The phase error is the same for all quantizers.

#### 3.3 Simulating the complete demodulator

The simulations described above were performed with the quantizer number-of-bits parameter ranging from 8 to 16; unfortunately, a converter capable of sampling at 8 MSa/s with 16-bit precision was not available commercially. The 14-bit converter used in the prototype system has a dynamic range exceeding the specified 70 dB [49]. The following simulations aimed to investigate the performance of the prototype demodulator in the radar system. The simulation parameters are therefore set to match the prototype Dacs board.

#### 3.3.1 Simulation parameters

#### 3.3.1.1 Dynamic range

The demodulator should have a minimum dynamic range of 70 dB; this translates into an input voltage ranging from 1  $V_{pk-pk}$  to 316.2  $\mu V_{pk-pk}$ . The smallest input has an amplitude of only a few quantizer steps ( $\Delta$  is 61  $\mu$ V when referred to the transformer input.) Simulations were performed for the maximum and minimum input amplitudes.

#### 3.3.1.2 Signal-to-noise ratio

The maximum signal-to-noise ratio at the transformer input was chosen as 80 dB, based on the radar receiver performance [5]. The thermal noise standard deviation was only  $\sigma_{th}$  =1.12  $\mu$ V, much smaller than the quantizer step size (referred to transformer input.) The signal-to-noise ratio with the smallest input was then 10 dB. The simulation was also performed for a noise

Figure 19. Simulated rms amplitude error versus N for  $\sigma_j=1x10^{-9}$

Figure 20. Simulated rms phase error versus N for  $\sigma_j=1x10^{-9}$

standard deviation of 70.5  $\mu$ V $_{pk-pk}$ , slightly larger than the quantizer step size; the signal-to-noise ratio was 74 dB with the maximum input and just 4 dB with the minimum input.

#### 3.3.1.3 Timing jitter

The frequency synthesizers used to generate the transmit and local oscillator signals have a worst-case rms phase noise of  $2.2^{\circ}$  [5]. Assuming the same instability in the IF signal, i.e.  $2.2^{\circ}$ , the rms phase noise in the 2 MHz input signal is 3.3ns. The Dacs prototype contains a 16 MHz Vectron TO-330 temperature-compensated crystal oscillator; integrating the phase noise over the 10 kHz bandwidth for which the manufacturer specifies it, we find that the rms timing jitter is less than 60 ps (Appendix A.) We consider phase noise to be effectively timing jitter, so the simulations were performed with a timing jitter parameter of  $\sigma_j = 2$  ns, 3 ns, and 4 ns - the simulation results should bound the achieved performance.

#### 3.3.2 Simulation results

The errors are nearly identical for both signal-to-noise ratios at the maximum input amplitude (see Table 3.) Coherent integration reduces the rms amplitude error towards an asymptote, more pronounced for larger timing jitter; this behaviour indicates that timing jitter is the most significant contributor of error - even at N=1024, the rms amplitude error is several times larger than the standard deviation of the thermal noise. This is not surprising, as (15) predicts a maximum voltage error of 12.5 mV when the input signal is sampled with timing jitter  $\epsilon_{tj}$  of 2ns; this is orders of magnitude greater than the magnitude of the thermal noise. The phase error also shows a clear dependence on the timing jitter, but is more reduced by coherent integration. Table 3 shows some of the results for A=999 mV $_{pk-pk}$  and  $\sigma_{tj}=3$  ns.

| SNR   | $\frac{\epsilon_{A,N=1}}{\epsilon_{A,N=1024}}$ | $\frac{\epsilon_{\phi,N=1}}{\epsilon_{\phi,N=1024}}$ | $\epsilon_{A,N=1}$ | $\epsilon_{A,N=1024}$ | $\epsilon_{\phi,N=1}$ | $\epsilon_{\phi,N=1024}$ |

|-------|------------------------------------------------|------------------------------------------------------|--------------------|-----------------------|-----------------------|--------------------------|

| 74 dB | 14.8                                           | 32.8                                                 | 5.9 mV             | $400~\mu V$           | 1.4°                  | 0.04°                    |

| 80 dB | 14.6                                           | 32.8                                                 | 5.8 mV             | 396 $\mu$ V           | 1.4°                  | $0.04^{\circ}$           |

Table 3. Rms error values for input amplitude of 499 mV and timing jitter std. dev. of 3 ns

In contrast, the rms error at the minimum signal amplitude depends strongly on signal-to-noise ratio, the errors for a SNR of 4 dB being about twice the magnitude of the errors for a SNR of 10 dB. The errors are the same for all three timing jitter values, in accordance with the prediction from (15) that the sample error is about 8  $\mu$ V when the input signal is sampled with timing jitter  $\epsilon_{tj}$  of 4ns - this is much smaller than the quantizer step size. Coherent integration improves both the rms amplitude and phase error by approximately 32 as N increases from 1 to 1024, matching

Figure 21. Simulated rms amplitude error; amplitude = 999 mV  $_{pk-pk}$  and SNR = 74 dB

Figure 22. Simulated rms phase error; amplitude = 999 mV  $_{pk-pk}$  and SNR = 74 dB

Figure 23. Simulated rms amplitude error; amplitude = 316  $\mu V_{pk-pk}$  and SNR = 10 dB

Figure 24. Simulated rms phase error; amplitude = 316  $\mu V_{pk-pk}$  and SNR = 10 dB

| SNR   | $\frac{\epsilon_{A,N=1}}{\epsilon_{A,N=1024}}$ | $\frac{\epsilon_{\phi,N=1}}{\epsilon_{\phi,N=1024}}$ | $\epsilon_{A,N=1}$ | $\epsilon_{A,N=1024}$ | $\epsilon_{\phi,N=1}$ | $\epsilon_{\phi,N=1024}$ |

|-------|------------------------------------------------|------------------------------------------------------|--------------------|-----------------------|-----------------------|--------------------------|

| 4 dB  | 31.7                                           | 37.1                                                 | 52 μV              | 1.6 μV                | 21°                   | 0.6°                     |

| 10 dB | 31.9                                           | 32.4                                                 | $28 \mu V$         | $1~\mu V$             | 10°                   | 0.3°                     |

Table 4. Rms error values for input amplitude of 158 uV and timing jitter std. dev. of 3 ns the theoretical improvement due to dithering; the dithering is effective even for the lower noise voltage (10 dB SNR.) Table 4 shows some of the results for A=316  $\mu$ V<sub>pk-pk</sub> and  $\sigma_{tj}$ =3 ns. The rms phase error is very large without coherent integration, as much as 21°, illustrating the sensitivity of the phase output when the input amplitude is only a few  $\Delta$ .

#### 3.4 Summary

Computer simulations were performed to determine the relationship between sampling errors and the accuracy of the digital quadrature demodulator output and the effectiveness of coherent integration in improving the accuracy. The discrete-time simulations were performed in Python and the results were analysed using Matlab.

The first series of simulations examined the effects of thermal noise and timing jitter in isolation. Coherent integration was found to reduce the output errors due to thermal noise, provided the noise standard deviation was at least an eighth of the quantizer step size. The reduction corresponded well to that predicted by (12). Timing jitter caused more severe errors, and coherent integration failed to reduce the amplitude error by the factor predicted as N increased. The amplitude and phase errors, moreover, were independent of the quantizer step size for jitter with standard deviation greater than 1 ns. The amplitude and phase errors were proportional to the timing jitter, as expected.

Simulation of the prototype demodulator driven with the radar IF and clock signals was intended to predict whether the required performance would be achieved. Timing jitter caused the predicted performance to fall short of the specification at the maximum input amplitude; the phase error exceeded the tolerance at the lowest input amplitude due to the relatively large quantizer step size.

The link between simulations of the demodulator performance and the prototype system has already been established in the last simulation series, which matched the simulation parameters to the prototype. The following chapter describes the design and implementation of the hardware, programmable logic, and software used to implement the demodulator, and describes the measurement of the prototype performance.

# Chapter 4 Design and implementation of the prototype

This chapter briefly describes the design and implementation of the Dacs circuit board and software. The Dacs board is placed in the context of the Venus radar system, and a brief requirements analysis is then elaborated. This is followed by a discussion of the design and implementation of the hardware, programmable logic, and software, which emphasizes the significant features. Finally, the performance of the digital quadrature demodulator is measured.

#### 4.1 Dacs in context of radar architecture

Figure 25. Architecture of the Venus radar system

The data capture system (Dacs) is one module of the Venus ground penetrating radar system. The Venus GPR uses a stepped frequency continuous wave architecture, described in more detail in Chapter 2. Most of the Venus radar's component systems have a single function. The Dacs unit, however, integrates several important functions onto one circuit card:

(1) Digital quadrature demodulation. The IF signal is digitised by synchronous sampling, and

- the sample sequence is then processed by special algorithms. These suppress some of the noise in the digitised signal and perform digital quadrature demodulation to extract the input signal's amplitude and phase.

- (2) *Radar control*. The Dacs controls the operation of the entire radar system by setting parameters of other systems in the radar, such as the frequency synthesizers and the downconverter. The Dacs also directs their operation.

- (3) *Communication*. An operator controls the radar using a computer connected to the Dacs board; the computer sends commands to the Dacs and receives status information and captured data.

#### 4.2 Statement of key user requirements

#### 4.2.1 Digital quadrature demodulation

#### 4.2.1.1 Profile rate

The data capture system must capture a minimum of 10 full profiles per second, with at least 100 frequency steps per profile. The ramp repetition interval (RRI) must therefore not exceed 100 ms, and the dwell time cannot exceed 1 ms. Amplitude and phase measurements of both the transmit-receive and the calibration channels must be taken at each frequency step.

#### 4.2.1.2 Dynamic range

The dynamic range must be at least 70 dB (this specification is derived from the Mercury radar [5]); the maximum allowed input voltage is 1  $V_{pk-pk}$ . The IF input impedance should be 500  $\Omega$  to ensure compatibility with the AD603 programmable gain amplifier which drives the IF signal input on the Dacs [25].

#### 4.2.1.3 Accuracy

The phase output should have a rms output error no larger than  $0.2^{\circ}$ ; this is the same as the error specification for the frequency synthesizers of the Mercury radar [5]. The rms amplitude error should be no larger than  $120~\mu\text{V}$ , which is equivalent to  $2\Delta$  (quantizer step size) for a 14-bit analogue-to-digital converter.

#### 4.2.2 System control

Dacs requires a microcontroller to implement system control and communications functions. The microcontroller software will execute from Flash memory and use SRAM as a temporary store. Although the microcontroller should eventually execute an operating system, targetting the microcontroller with code written in C is sufficient for test purposes. Only the functions necessary for testing the digital quadrature demodulator will be implemented.

#### 4.2.3 Communication

The Dacs must communicate with other systems in the radar through a backplane interface. These systems include the two frequency synthesizers, the RF/IF board (downconverter), and the RF/IF motherboard. These functions will not be implemented on the prototype.

#### 4.2.4 Electro-mechanical

Each system of the radar, including the Dacs, must be contained on an Eurocard-sized circuit board. The circuit board will be mounted onto a backplane in the enclosure.

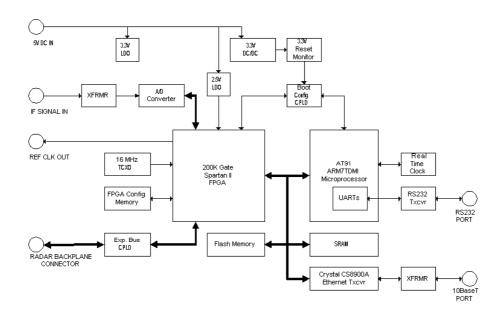

#### 4.3 System design

The data capture system consists of a printed circuit board populated with semiconductor and passive components. The functionality of the programmable logic devices is described in VHDL, and the software running on the microcontroller is written in C. Both the programmable logic devices and the microcontroller and its flash memory are programmed in-circuit.

The components can be grouped by function, as in Figure 26, which depicts only the major modules.

#### 4.4 Hardware design and implementation

#### 4.4.1 Design

#### 4.4.1.1 Analogue-to-digital conversion

The ADC device was selected on the basis of resolution and sampling speed. A survey of available devices indicated that the fastest 16-bit converters, from Maxim and Analog Devices, ran at a sampling rate of 1 MSa/s - not fast enough for this application [50][51]. So a 14-bit analogue-to-digital converter was specified.

The Texas Instruments THS1408 is a 14-bit differential-input ADC and includes a programmable gain amplifier (PGA) with gain adjustable from 0 to 7 dB, and samples at speeds up to 8 MSa/s [49, p 5]. The ADC has a pipeline latency of 9.5 periods; ambiguity in dividing the reference clock makes the latency irrelevant. The THS1408 contains several control registers, which allow a programmable offset to be subtracted from the sample value and the PGA gain to be set.

A centre-tapped transformer converts the single-ended IF signal into a suitable differential signal. The maximum IF input is 1  $V_{pk-pk}$  ac, producing a 4  $V_{pk-pk}$  signal at the ADC input; the

Figure 26. Function blocks of the data capture system

Figure 27. Block diagram of the Dacs hardware

quantizer step size is thus 61  $\mu$ V referred to the transformer input. The datasheet for the THS1408 specifies a typical spurious-free dynamic range as 80 dB, for  $f_{in}=4$  MHz and  $f_s=8$  MHz [49].

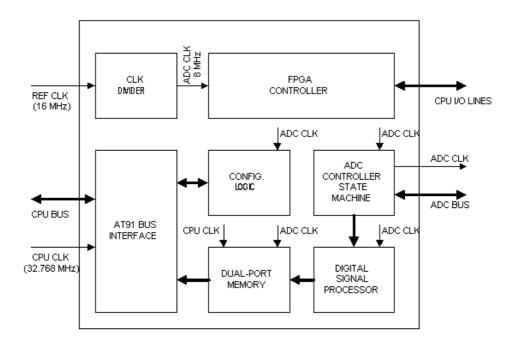

#### 4.4.1.2 Digital signal processing in the FPGA

The digital signal processing is performed in a Xilinx Spartan-II field-programmable gate array with 200,000 gates. The processing modules are coded in VHDL and loaded into the FPGA chip after power is applied.

#### 4.4.1.3 Reference clock for digital quadrature demodulator

The Dacs design provides three sources of reference clock for the demodulator. The first two are on-board oscillators: a 16 MHz temperature-compensated crystal oscillator (TCXO) or a 32 MHz crystal oscillator. A connector provides an input port for an external oscillator, such as the HP 33120A signal generator used during testing.

#### 4.4.1.4 Microcontroller controls system operation

The Dacs board contains an Atmel AT91M40400 microcontroller, which integrates an ARM7TDMI processor core, several on-chip peripheral devices, and a 16-bit external bus interface. The microcontroller boots off a 512K x 16-bit flash memory IC, and uses an 256K x 16-bit SRAM chip for temporary storage. The AT91M40400 executes 32-bit instructions, but the external bus interface is 16-bit so the processor executes instructions at half the bus rate.

#### 4.4.1.5 Bootstrap configuration CPLD

A small CPLD (Xilinx XC9572) controls the boot mode of the microcontroller; this CPLD routes several signals between peripheral devices, the microcontroller, and the FPGA.

#### 4.4.1.6 Communication interfaces

The Dacs board has several communication ports, linking it with other components of the radar system and with external devices. The Dacs board has two serial ports: one is implemented as an RS232 serial port, the other is a slot requiring a special add-on transceiver card. These serial ports provide a simple interface to external computers. A Crystal CS8900A Ethernet transceiver chip implements a 10BaseT Ethernet port, but was not placed on the prototype. The expansion bus interface is based on the 16-bit ISA synchronous bus; this is the link to other systems within the radar enclosure, which share a common backplane, and was also not placed on the prototype.

#### 4.4.2 Implementation

The hardware design was captured as a set of schematic diagrams in Protel 99SE. The artwork for the printed circuit board was also drawn in Protel 99SE, and sent to a PCB production house, Trax InterConnect (Pty) Ltd, who fabricated the circuit boards to specification - it is worth noting that the printed circuit board stretched the limits of the available fabrication technology, especially in terms of via size and track width/spacing in certain sections. The bare circuit board was populated by another contractor, Rhomco (Pty) Ltd.

#### 4.5 Programmable logic design and implementation

The Dacs board contains three programmable logic devices: an FPGA used mainly for signal processing, a small CPLD assisting with boostrap configuration, and a large CPLD used for the expansion bus interface. Firmware was not produced for the expansion bus as this was outside the thesis scope.

#### 4.5.1 Programmable logic implemented in the bootstrap configuration CPLD

The logic within the configuration CPLD is implemented as simple combinatorial logic. It configures the microcontroller boot mode at power-on, configures the FPGA programming mode at power-on, routes IO signals between the microcontroller, FPGA, and CS8900A Ethernet transceiver, and performs some simple logic functions on the reset signals.

#### 4.5.2 Programmable logic implemented in the FPGA

The prototype board was used to test the demodulator, and was not integrated into the radar. The Dacs prototype was therefore programmed to take a sequence of measurements at a constant input amplitude and phase.

#### **4.5.2.1** Structure

The functions implemented in the FPGA were decomposed into modules defined in terms of their behaviour and interfaces. This top-down design approach provided similar advantages to an object-oriented approach to software: reduced coupling between modules made modifications simpler, there was a clear mapping between modules and their functions, and the completed modules lend themselves to reuse [52].

Controller for analogue-to-digital converter The ADC controller is the interface between the FPGA and the ADC chip: it loads configuration parameters into the ADC, and reads sample values from the ADC, over a half-duplex, parallel bus. The ADC amplifier gain, the programmable offset, and the control register can be set.

**Digital signal processor** The digital signal processor acts as an accumulator, the first step in

Figure 28. Block diagram of the VHDL code for the FPGA